Voici un système de capture en noir et blanc, permettant l’acquisition d’images provenant d’une caméra ou d’un magnétoscope. Les images sont visibles sur l’écran du PC, de façon cyclique ou par instantanés, sous contrôle d’un logiciel tournant sous Windows.

Il n’est pas nécessaire de préciser que l’électronique est en continuelle évolution dans tous les domaines.

Scanner, webcam, ou grabber ?

Un secteur d’application extrêmement intéressant est celui qui concerne l’acquisition et le traitement d’images, et plus particulièrement les signaux vidéo, eu égard à la croissante nécessité de faire aujourd’hui avec l’ordinateur ce qu’autrefois se faisait avec les appareils photo, les chambres noires et les pellicules argentiques.

Une fois disponible sous forme de “bits”, l’image peut être “traitée”, c’est-à-dire utilisée pour faire de tout.

Par exemple : elle peut être retouchée, superposée à une autre, modifiée, envoyée par voie télématique, et subir un tas d’autres traitements.

Le but des “digitaliseurs” consiste à convertir une image analogique en format numérique. Autrement dit : à la présenter sous forme de bits.

Les systèmes d’acquisition d’images sont nombreux et différents les uns des autres en fonction de ce à quoi ils doivent servir.

S’il s’agit, par exemple, de saisir une photo en ordinateur, le plus simple est de faire appel à un scanner.

Si l’on veut saisir des images, ce n’est plus au scanner qu’il convient de faire appel, mais plutôt à une webcam, ou à un appareil photo numérique.

Si, par contre, l’application demande de capturer un photogramme, ou les images d’un film issues d’une caméra ou d’un magnétoscope, alors, les appareils qui conviennent ne sont plus, ni le scanner, ni la webcam, ni l’appareil photo numérique.

Ce qu’il faut dans ces cas, est le “grabber”.

Qu’est-ce qu’un “grabber” ?

Pratiquement, il s’agit d’un appareil capable de capturer (to grab) et de mémoriser le signal vidéo composite provenant d’une caméra télé, de décomposer chaque photogramme (frame), et de porter l’image à l’écran.

Vue l’énorme potentialité d’un tel appareil, nous avons pensé mettre au point un système d’acquisition d’images pour PC, relativement simple, qui ouvrira la route à une série de projets du même style, liés au monde de la sécurité et de la surveillance, tous innovants.

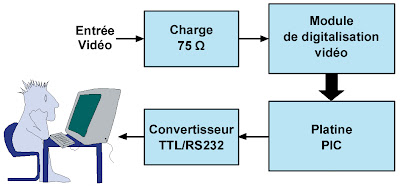

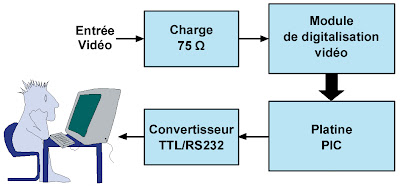

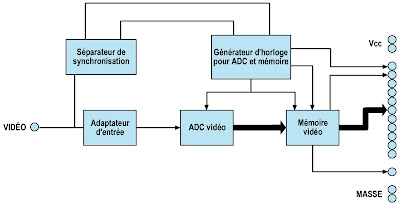

En fait, l’analyseur vidéo par lequel nous commençons et que nous vous présentons ce mois-ci, est formé - à plus proprement parler - de deux sous-ensembles : un “grabber” et un module d’interface aux normes RS232-C assurant la liaison au port série du PC (figure 1).

Le grabber est néanmoins le coeur de l’appareil.

Il s’agit de l’élément qui capture le signal vidéo, l’échantillonne, et stocke en mémoire vive (RAM adaptée) un photogramme à la fois, c’est-à-dire chaque frame (image instantanée) d’une prise de vue.

Ce module s’occupe du déroulement de toutes les opérations, mémorise, et extrait de la RAM les données sur 8 bits en parallèle.

En association à cet ensemble, il y en a un autre, que nous appelons “unité de contrôle”, qui dialogue avec le “grabber” par son bus, et accomplie différentes fonctions.

Il s’occupe de l’acquisition du signal vidéo composite, balaye (moyennant un signal d’horloge que lui-même génère) les données de la mémoire, les extrait, et convertit les informations ainsi obtenues en format série, c’est-à-dire en impulsions qu’il envoie au PC auquel il est relié et dont il reçoit, tour à tour, les commandes relatives à ce qu’il doit faire.

Le tout, sous contrôle d’un logiciel écrit pour fonctionner en environnement Windows 95/98, comportant une interface visuelle constituée, en grande partie, par un écran virtuel dans lequel apparaissent les images mémorisées, à savoir : les images capturées.

Sur l’interface visuelle, il existe des boutons et des cases à cocher, un pour chaque tâche que l’on veut accomplir : capturer une image passant à l’écran à un moment donné, la mémoriser (en format bitmap), sortir du programme… ou encore : choisir la résolution de l’image (élevée ou faible), sélectionner les tons de gris, incruster dans l’image la date et l’heure.

Celui que nous avons appelé le coeur du circuit (le “grabber”), à savoir le module assurant la capture vidéo, nous le retrouverons dans d’autres projets, que nous préparons pour les présenter à l’avenir, adaptés à d’autres usages.

Commençons donc par voir comment celui-ci fonctionne, et remettons à plus tard l’examen de l’interface et du logiciel de gestion.

Le “grabber”

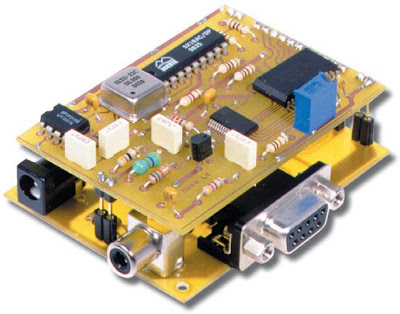

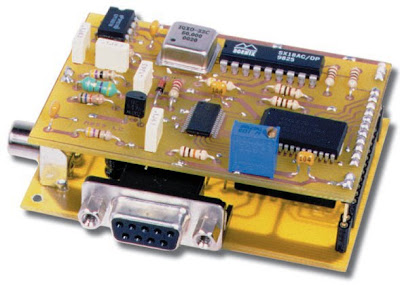

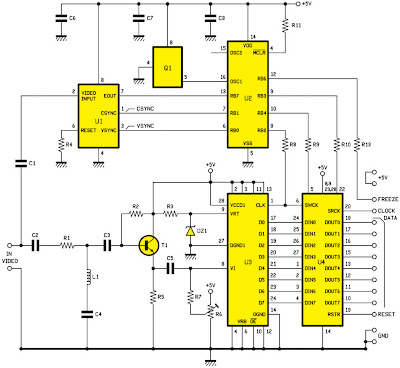

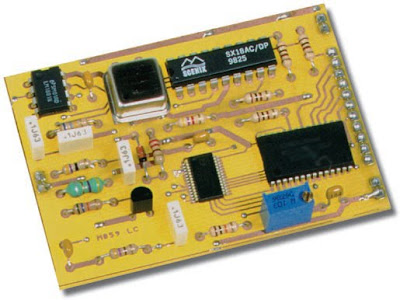

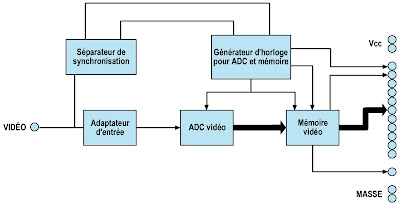

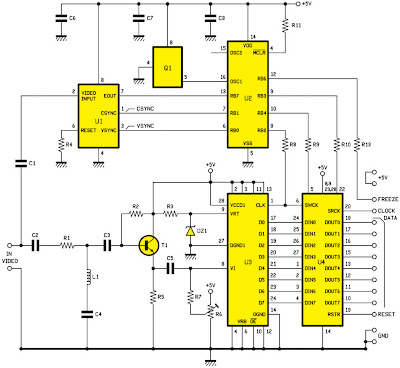

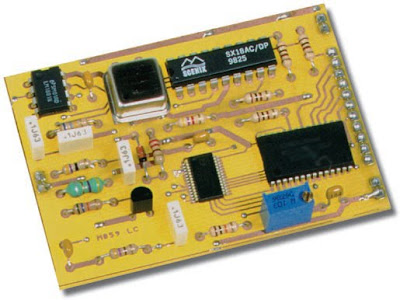

Le grabber, autrement dit le sousensemble qui effectue la digitalisation, dont le schéma électrique est visible en figure 2 et le schéma synoptique en figure 3, se présente sous la forme d’une carte (voir figures 9 et 10) pourvue de 15 points de contact, destinés à s’interconnecter à l’unité de contrôle (voir figures 14 et 15) et de deux points de contact constituant l’entrée du signal vidéo.

En gros, il échantillonne la grandeur présente sur son entrée, mémorise les données relatives à chaque pixel dans une RAM spéciale (voir figure 4) puis active une mémoire tampon dont la capacité permet de contenir un photogramme entier, de sorte à permettre au module d’interface d’y venir chercher les données, pour les décharger à son rythme vers le PC.

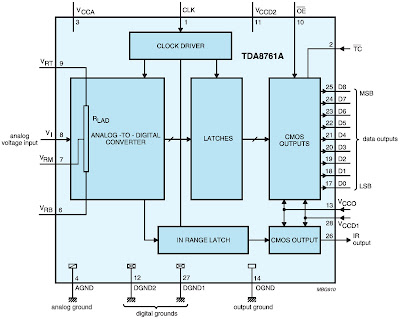

L’échantillonnage est effectué par un convertisseur A/D à 8 bits (voir figure 5).

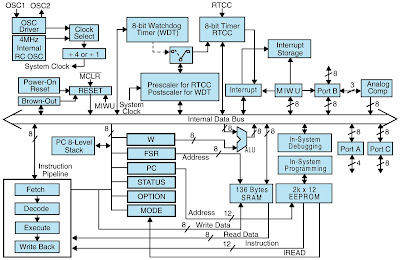

Tout le module est géré par un microcontrôleur haut de gamme, à savoir un SCENIX SX18 (voir figure 6), capable de travailler à une fréquence d’horloge de 50 MHz, issue d’un résonateur DIL intégré (référencé Q1 dans le schéma) et arrivant sur la broche 5.

Le rôle de ce microcontrôleur est très important.

Il génère, entre autres, le signal d’horloge au rythme duquel le convertisseur A/D effectue les échantillonnages, et synchronise - sur ce même rythme - la mise en mémoire d’une image dans la portion de RAM réservée à l’écriture.

En effet, le signal servant d’horloge au convertisseur, qui correspond au WCK (Write ClocK), cadence, au même rythme, le convertisseur A/D (broche 1 de U3) et la mémoire (broche 6 de U4).

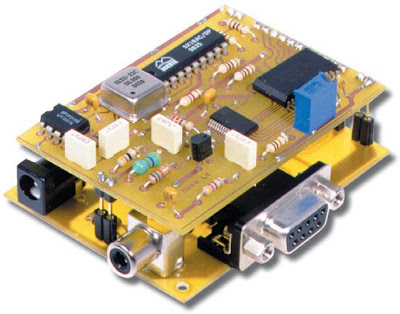

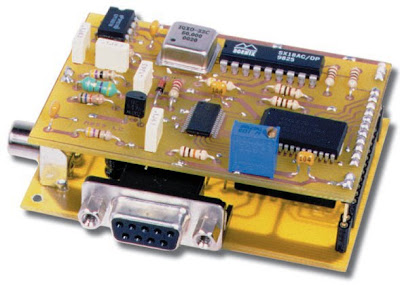

Figure 1 : Une autre vue d’un des prototypes prêt à fonctionner.

Figure 1 : Une autre vue d’un des prototypes prêt à fonctionner.

Une RAM à deux “pages”

Un autre rôle important du microcontrôleur est la gestion du partage de la RAM en deux “pages”, c’est-à-dire en deux blocs virtuels : un dans lequel le convertisseur analogique/digital écrit les octets correspondant à chaque pixel et l’autre dans lequel l’interface de sortie (représentée par la deuxième carte) peut lire à tout moment, soit en temps réel, soit lors de l’arrêt d’une acquisition (commandée au moyen de la ligne FREEZE du bus).

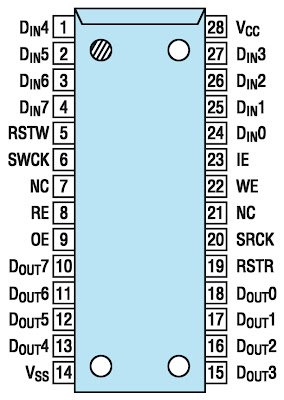

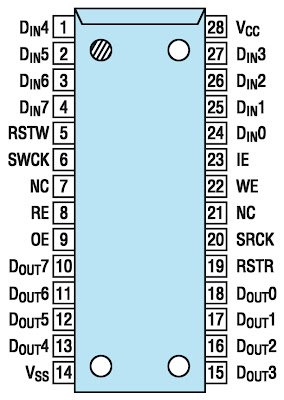

Ceci explique (voir figure 4) pourquoi la mémoire (une AL422 fabriquée par la société AVER LOGIC) dispose de commandes en double, dont deux lignes d’horloge séparées (une pour l’écriture, appelée WCK = Write ClocK, et une pour la lecture, appelée RCK = Read ClocK), et deux lignes de Reset séparées (une ligne de Reset pour l’écriture, appelée WRST = Write ReSeT, et une ligne de Reset pour la lecture, appelée RRST = Read ReSeT).

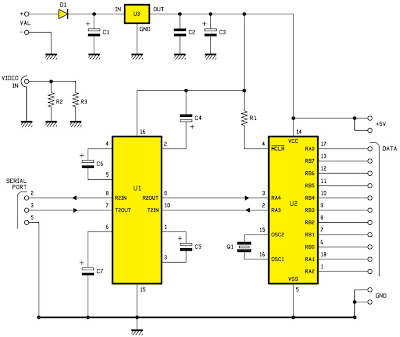

Le module d’interface

Le module d’interface consiste en une carte qui s’interconnecte avec le module digitaliseur au moyen de picots enfichables. Par ce biais, les deux modules se partagent non seulement les lignes d’alimentation, mais aussi le bus de données, les lignes de Reset, le signal d’horloge de la RAM U4, et celui du FREEZE du SCENIX.

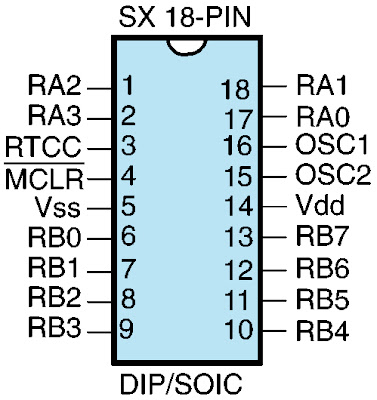

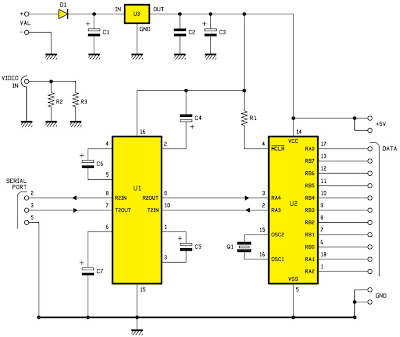

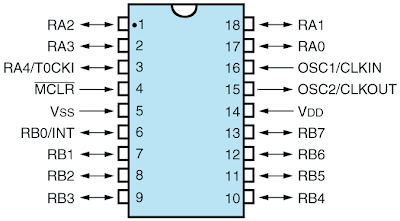

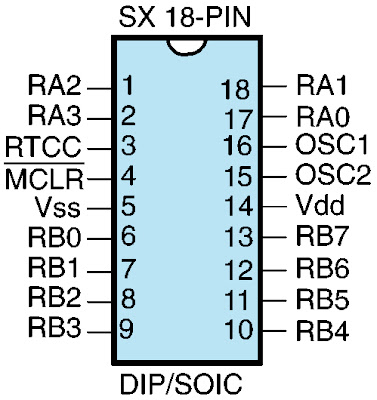

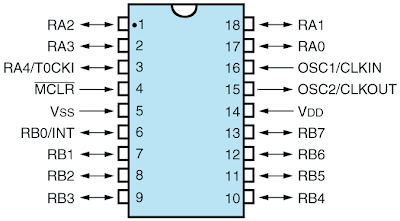

Il est entièrement ramassé autour du microcontrôleur PIC 16F84, auquel s’ajoute juste un convertisseur TTL/RS232 bidirectionnel pour communiquer avec le PC par le port série.

Il suffit de regarder son schéma électrique pour en constater l’extrême simplicité.

Le microcontrôleur en est le coeur.

Celui-ci est exploité au plein de ses capacités, car toutes les lignes de port sont utilisées : les 8 lignes du port B (B0, B1, B2, B3, B4, B5, B6 et B7), initialisées en entrées, constituent le bus par lequel il lit les données, autrement dit, la voie par laquelle il prélève, octet après octet, les images digitalisées par le convertisseur A/D.

Du côté du port A, deux lignes servent à la liaison série, tandis qu’A0, A1 et A2 sont configurées en sorties et servent à contrôler les lignes FREEZE, Clock et Reset de la partie lecture de la RAM à deux pages.

L’alimentation de l’ensemble des circuits est obtenue en stabilisant à 5 volts la tension continue portée sur le connecteur VAL. La diode D1 protège contre les risques d’inversion de polarités.

Pour obtenir les 5 volts stabilisés, on fait appel à un classique 7805.

Les condensateurs qui l’entourent, filtrent l’alimentation d’éventuels signaux parasites pouvant provenir de l’extérieur, et surtout des transitoires générées tout particulièrement par le module digitaliseur, lequel travaille à des fréquences très élevées. U1 assure l’interface avec le PC. Il met en oeuvre un MAX232 qui rend compatibles les signaux du port série, fournis au standard RS232-C (impulsions variant entre +12 volts et –12 volts), à ceux utilisés par les différents circuits logiques (0-5 volts) et par les microcontrôleurs, dans les échanges qui ont lieu entre le PC et les modules, et inversement.

La communication série se fait à la vitesse de 57 600 bps (bits par seconde), ce qui suppose que le PC à utiliser doit disposer d’un UART (Universal Asynchronous Receiver Transmitter) convertisseur série/parallèle et parallèle/série, rapide (16550 compatible, ou supérieur).

Mais voyons ce qui ce passe exactement dans le circuit à partir du moment où il est mis sous tension.

Figure 2 : Schéma électrique du module digitaliseur.

Figure 2 : Schéma électrique du module digitaliseur.

Synoptique complet du digitaliseur

Voulant résumer, on peut dire que le microcontrôleur du module d’interface (un PIC 16F84) interroge cycliquement le bus de sortie du digitaliseur, arrête le balayage après l’exploration complète d’une image, et décharge ensuite les données mémorisées jusque-là.

Mais, procédons en ordre, et voyons plus en détail ce que ce module fait exactement.

Lorsque, à la demande du PC, le microcontrôleur du module d’interface doit transmettre une image digitalisée, il met à l’état bas la ligne aboutissant au FREEZE.

Ainsi faisant, le PIC demande au microcontrôleur du module digitaliseur (le SCENIX) de s’arrêter au terme du balayage du photogramme en cours de transmission.

Le pas suivant est celui qui concerne la génération du signal d’horloge cadençant l’extraction des octets qui sont en fait la mémorisation de l’état de chaque pixel de l’image.

Mais, avant cela, pour être sûrs que l’image soit extraite correctement, le PIC déclenche un Reset sur la ligne de bus aboutissant au RSTR, lequel remet à zéro le compteur d’adresses de la RAM U4 implantée sur le module digitaliseur.

Puis, à chaque impulsion d’horloge, il lit l’octet correspondant, le convertit en format série, lui ajoute les bits de start et de stop (pas celui de parité, car la communication avec le PC a lieu sans contrôle de parité), et l’envoie à l’RXD de la porte RS232-C du PC, où il est lu et traité par un logiciel tournant sous Windows.

Une fois que tous les 120000 octets ont été balayés, on remet à 1 la ligne FREEZE et on bloque l’horloge.

A partir de là, le digitaliseur reprend à mémoriser le signal vidéo.

Le programme de gestion permet de choisir entre une résolution faible et une élevée (voir figure S).

En terme de pixels, la faible résolution correspond à des images en format 200 x 150 points, tandis que la haute résolution correspond à des images en format 400 x 300 points.

Lorsqu’on a opté pour des images à faible résolution, la fréquence d’horloge que le PIC envoie à la mémoire est divisée par quatre, par rapport à la fréquence nominale, car - dans ce cas - seulement un quart des points constitutifs d’une image sont à lire.

L’image envoyée au PC, octet après octet, est alors sensiblement plus petite. Mais, pour éviter de restituer à l’écran une image en petit format, le logiciel effectue un “resizing”.

Cela remet l’image au bon format, en tenant compte évidemment du facteur de division demandé, lequel n’est rien d’autre que le taux choisi pour la résolution.

Quant à la sélection des tons de gris, elle aussi se fait au moyen de l’interface graphique.

Cela revient à indiquer le nombre de bits que l’on veut utiliser pour la mémorisation des pixels.

En sachant que le convertisseur A/D numérise chaque point d’image avec une définition de 8 bits, il en résulte une échelle de 256 niveaux de gris possibles.

Si l’utilisateur choisit une résolution à 256 niveaux, les données sont transformées au rythme d’un octet par pixel ; tandis que s’il choisit seulement 16 niveaux, une sorte de compression est opérée qui conduit le digitaliseur à numériser sur seulement 4 bits.

A ce point, faisons les comptes : le temps nécessaire au PC pour reconstituer une image à faible résolution (200 x 150 pixels) avec seulement 16 niveaux de gris, est d’environ 7 secondes ; tandis que pour reconstituer une image en résolution 400 x 300 pixels avec le même nombre de niveaux de gris, le PC a besoin de 20 secondes.

Considérons maintenant le cas d’une image toujours en définition 200 x 150 points, mais avec 256 niveaux de gris : le PC a besoin de 12 secondes, et pour reconstituer une image à la plus haute résolution et avec le maximum de niveaux de gris (256), il lui faut 35 secondes.

Le module vidéo

Figure 3a.

Figure 3b.

Figure 3: Le module vidéo, schéma synoptique (3a) et photo d’un prototype terminé (3b).

Le “grabber”, véritable coeur de l’appareil, est l’élément qui digitalise le signal vidéo.

Il se présente sous la forme d’une carte pourvue de 15 points de contact destinés à s’interconnecter à d’autres unités de contrôle, et de deux points de contact destinés à recevoir le signal vidéo.

Brièvement présenté, les tâches qui lui sont dévolues se résument ainsi : il échantillonne la grandeur présente sur son entrée, mémorise dans une RAM spéciale les données relatives à chaque pixel, puis active une mémoire tampon (contenant un photogramme complet) d’où l’on peut ensuite extraire les données en forme série.

L’échantillonnage est effectué par un convertisseur A/D à 8 bits, qui stocke les données dans une RAM de 3 Mo.

Toutes les opérations s’effectuent sous le contrôle d’un microcontrôleur SCENIX SX18 travaillant à 50 MHz.

La RAM vidéo

Figure 4 : La RAM vidéo.

Figure 4 : La RAM vidéo.

Les données échantillonnées par le convertisseur A/D sont stockées dans une DRAM (RAM dynamique) AL422 de 3 mégabits en format 384 K x 8 bits, fabriquée par AVER LOGIC.

La particularité de cette RAM, outre son extrême rapidité (temps d’accès inférieur à 15 ns), est de posséder pas mal de choses en double: deux lignes d’horloge séparées: une pour l’écriture (WCK = Write ClocK) et une pour la lecture (RCK = Read ClocK) ; deux lignes de Reset séparées : WRST (Write ReSeT) et RRST (Read ReSeT) ; et enfin deux bus de données séparés, chacun de 8 bits : un bus pour les données qui entrent, et un autre pour les données qui sortent.

Le buffer de la mémoire (celui qui stocke les données relatives à chaque image) est du type FIFO (First In, First Out) capable de contenir 819 x 480 bytes.

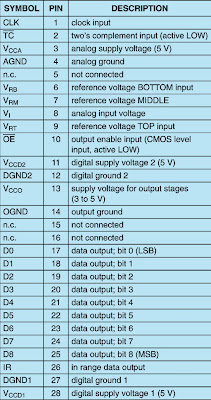

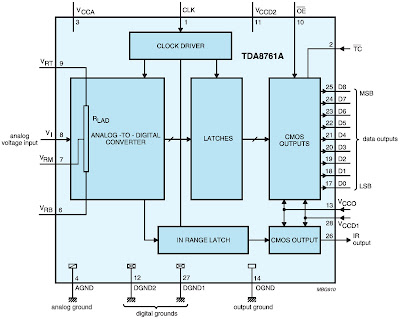

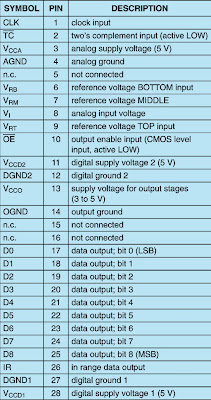

Le convertisseur AD pour signaux vidéo

Figure 5a.

Figure 5b.

Figure 5c.

Figure 5: Le convertisseur AD pour signaux vidéo.

Le schéma synoptique est donné en figure 5a, le rôle de chaque broche en 5b et le brochage lui-même en 5c.

Ce convertisseur a un rôle de tout premier plan dans notre application. Il s’agit d’un conver tisseur à 9 bits TDA8761 fabriqué par Philips, dont - pour raisons de compatibilité - nous n’en utilisons que 8.

Devant échantillonner un signal vidéo composite, dont la largeur de bande est typiquement de 5,5 MHz, il travaille à la fréquence de 40 MHz.

A l’intérieur de ce circuit on trouve un convertisseur à mailles R/2R, un latch contenant les données échantillonnées et successivement transférées dans le buffer de sor tie, un clock et les nécessaires circuits relatifs à la logique de contrôle.

La conversion démarre en présence d’une impulsion positive sur la broche 1 (CLK).

Les données en format 8 bits, issues de l’échantillonnage de la grandeur lue à l’entrée (broche 8, VI), passent dans le latch, puis d’ici dans le buffer CMOS (toujours actif, car nous avons relié la broche 10 Output Enable à la masse), et enfin sortent par les broches 17 à 25.

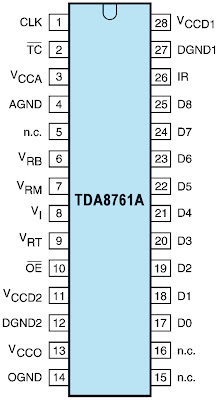

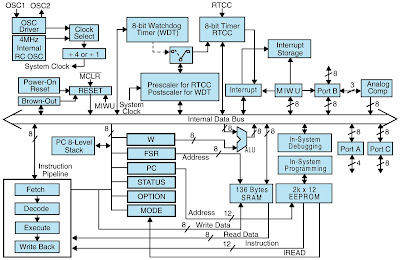

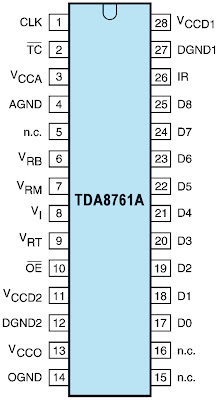

Le microcontrôleur SCENIX SX18

Figure 6a.

Figure 6b.

Figure 6: Le microcontrôleur SCENIX

Structure interne (6a) et brochage (6b) du microcontrôleur SCENIX SX18AC/DP en boîtier DIP18. Ce type de microcontrôleur peut travailler à une vitesse d’horloge pouvant aller jusqu’à 50 MHz.

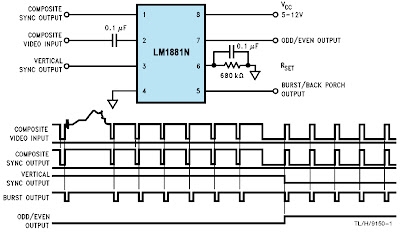

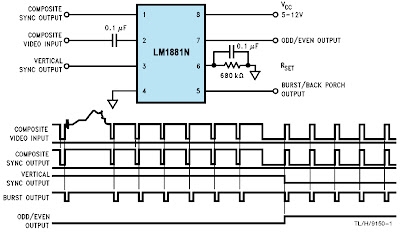

Figure 7 : Le séparateur de tops synchro.

Figure 7 : Le séparateur de tops synchro.

Pour cadencer le microcontrôleur SCENIX à la vitesse du signal vidéo composite présent à l’entrée du module d’acquisition, nous avons extrait les tops de ligne et de trame d’un circuit expressément étudié pour. Il s’agit du LM1881 de National Semiconductor, équivalent au EL4581 de ELANTEC, dans lequel, de précis circuits à seuil opèrent les filtrages nécessaires et fournissent les signaux primaires séparément.

Analyse du circuit

Le microcontrôleur commence par initialiser ses lignes d’entrée/sortie. Les lignes de port B0 et B1 sont configurées comme entrées, car c’est sur ces lignes que vont arriver les tops de ligne et de trame provenant de U1 (voir figure 7).

Les lignes B2, B3 et B4 sont configurées comme sorties ; elles sont destinées - respectivement - l’une à fournir le signal d’horloge (PIXCLK) qui synchronise la RAM et le convertisseur A/D, l’autre à gérer le Reset de la section mémoire destinée à l’écriture (le Reset de la “page” lecture est contrôlé par le bus…), et l’autre à commander la broche R/W de la RAM. La ligne B6 est configurée en entrée : elle lit la commande FREEZE provenant du module d’interface, commande que nous décrirons plus en avant. Enfin, la ligne B6, configurée elle aussi en entrée, reçoit les impulsions de la broche 7 (ODD/EVEN) de U1.

Le microcontrôleur est alimenté par les broches 14 (+5 volts) et 5 (masse), et travaille au rythme du signal d’horloge que le résonateur intégré lui envoie sur la broche 16.

Après la phase d’initialisation, il se synchronise avec les tops de trame et de ligne contenus dans le signal vidéo composite arrivant sur l’entrée (IN VIDEO) et que le séparateur de tops de synchronisations U1 extrait.

Ainsi scindés, ces deux signaux servent à reconstituer la trame de l’image initiale, à laquelle, cependant, on retire un certain nombre de lignes, dans le but de réduire la quantité de mémoire nécessaire à stocker chaque photogramme.

Plus exactement, le top de synchronisation de trame est utilisé pour le rafraîchissement de la mémoire et pour signaler au microcontrôleur à quel moment précis se termine l’acquisition d’un photogramme, tandis que le top de synchro ligne ser t à cadencer le convertisseur A/D et la mémoire, car il renseigne du moment auquel chaque ligne commence et finit.

Autrement dit : le microcontrôleur récupère - à partir du balayage horizontal - le pixel-clock (PIXCLK) qu’il envoie à la fois sur le convertisseur A/D et sur la partie RAM réservée à l’écriture (WCK), et - à partir du balayage vertical - l’information lui indiquant précisément à quel moment se termine l’écriture d’un photogramme dans la RAM.

C’est cette dernière information qui permet notamment la suppression des balayages de retour (flyback) qu’il n’aurait aucun sens de mémoriser.

Ainsi que nous l’avons laissé entendre plus haut, étant donné qu’il faut composer avec l’espace mémoire disponible, certaines lignes sont retirées de l’image, de sorte à limiter chaque photogramme au format max de 400 x 300 pixels (400 pixels en horizontale et 300 pixels en ver ticale). Ce qui conduit à une définition totale de 120 000 pixels.

Chaque pixel, ou point élémentaire d’image, est mémorisé à une fréquence de ligne d’environ 5 MHz. Et comme cette même fréquence, synthétisée par U2, cadence aussi les pas de la conversion A/D, la parfaite synchronisation entre celle-ci et celle du signal vidéo, garantit que la capture et la mémorisation en RAM des pixels de chaque ligne commence exactement au moment où celles-ci prennent naissance.

Puisque le clock qui pilote le convertisseur A/D agit aussi sur l’entrée WCK, les informations échantillonnées sont transférées dans la portion de RAM destinée à l’écriture, au même rythme et en parfaite correspondance.

Voyons plus en détail comment vont les choses.

Au démarrage d’une trame, le séparateur de tops synchro fournit au microcontrôleur une impulsion que celui-ci utilise pour effacer la mémoire (via WRST) et pour commencer à compter les cases mémoire, à partir de la case zéro.

Pendant ce temps-là, U3 est inopérant, jusqu’à ce que le microcontrôleur lui envoie une impulsion d’horloge, obtenue par U1, par extraction du top départ de la synchro horizontale contenu dans le signal vidéo composite.

A l’arrivée de cette impulsion, le convertisseur A/D lit le signal qui arrive sur son entrée (broche 3) et, au moment opportun (moment déterminé par le microcontrôleur, c’est-à-dire juste après le balayage de retour, que nous avons nommé flyback) échantillonne le niveau analogique correspondant au premier pixel, et le convertit en format digital sur 8 bits. Il s’ensuit un octet aussitôt écrit en RAM, car le même signal d’horloge qui incrémente la conversion A/D, incrémente aussi, en même temps, les adresses de la RAM. C’est ainsi que l’octet contenant l’information relative au premier pixel de la première ligne est écrit dans la première case mémoire.

Puis arrive la deuxième impulsion : le convertisseur l’échantillonne et envoie en RAM l’octet relatif au deuxième pixel.

Puis, à la troisième impulsion, il fait de même avec le troisième octet… et ainsi de suite, jusqu’au 400e.

A ce moment, la première ligne a été échantillonnée et mémorisée. On passe à la ligne suivante.

Une fois que les 300 lignes constituant une page écran entière sont passées, les 120 000 cases RAM ont été remplies: une case par pixel.

Un photogramme complet a ainsi été mémorisé.

C’est alors qu’un nouveau top de synchronisation verticale arrive au microcontrôleur. Celui-ci envoie un Reset à la RAM, de sorte que les nouvelles données que le convertisseur A/D enverra en mémoire à partir de maintenant, soient écrites à partir de la première case mémoire, et se réfèrent à une nouvelle image.

Recommence ainsi un nouveau cycle : le convertisseur digitalise un pixel et envoie un (nouveau) premier octet, qui est stocké dans la case mémoire 1, etc.

Les nouvelles données écrasent les précédentes, dont elles prennent la place, après que le Reset ait fait table rase de ce que la RAM contenait précédemment.

Toute nouvelle ligne de l’image successive remplace le contenu de l’image précédente. Ce détail est important, car il détermine le résultat que l’utilisateur peut obtenir ; résultat qui dépend de la façon dont on lit le buffer.

Si la lecture est demandée en temps réel, le système restitue une série d’informations reconstituant exactement la page écran mémorisée.

Si par contre la lecture est plus lente que la mémorisation, les données que le buffer délivre ne correspondent pas à une entière séquence de digitalisation.

Pour cette raison il peut être utile de se servir de l’option arrêt sur image.

Dans ce cas, c’est la fin d’un photogramme qui déclenche le vidage du buffer.

Les informations que celui-ci contient sont alors mises sur le bus de données (indiquées par DATA sur le schéma) et le module d’interface, dont le schéma électrique est donné en figure 12, peut élaborer des signaux (voir figure 18) qui, portés à l’écran, restituent l’image capturée au moment voulu.

Conclusion : pour éviter de déclencher des lectures trop hâtivement, il convient de gérer avec discernement la ligne FREEZE.

Normalement, cette ligne doit être maintenue à l’état haut.

Si elle est mise à zéro, le microcontrôleur arrête toute scrutation, bloque le pixelclock, et - par voie de conséquence - l’écriture en RAM de toute nouvelle donnée.

Le microcontrôleur prend ensuite le contenu des 120000 adresses contenant le photogramme et le transfère dans la page de sortie de la RAM, d’où le module d’interface, sous le contrôle du microcontrôleur PIC16F84 (voir figure 13), peut le saisir via le bus de données, au rythme d’une horloge indépendante.

Figure 8: Vue sur le microcontrôleur SX18 et sur la RAM vidéo AL422.

Figure 8: Vue sur le microcontrôleur SX18 et sur la RAM vidéo AL422.

Images cohérentes

Il convient de préciser que lorsque la ligne FREEZE est portée au niveau bas, l’acquisition ne s’arrête pas inconditionnellement, car sinon l’interface déverserait sur le bus non pas des données se rappor tant à une unique image, mais des données restituant des morceaux d’images mélangées.

On aurait à l’écran une image composée en partie par des lignes provenant de la mise en mémoire de l’image précédente, et - pour une autre partie - de lignes provenant de l’image dont la capture était en cours d’acquisition avant l’arrêt forcé.

C’est pourquoi, le microcontrôleur va toujours jusqu’au bout dans la digitalisation d’une image, et n’arrête le convertisseur A/D et l’incrémentation de la RAM qu’après avoir mémorisé tous les pixels d’une image, et c’est seulement au terme de cette procédure qu’il met au repos la ligne du pixelclock.

Ainsi faisant, on a la certitude que les données extraites par U4 se rapportent toutes à la même image.

Lorsqu’on parle d’horloge, au cours d’une opération d’écriture en mémoire, l’on se réfère au signal que l’interface fait parvenir à la broche 20 de la RAM.

Autrement dit, à la ligne CLOCK du bus.

C’est à ce point que nous pouvons revenir sur ce à quoi nous avions fait allusion plus haut ; à savoir : la totale indépendance entre les deux pages de la RAM: celle d’écriture, et celle de lecture, pourvues - chacune - de son propre clock et de son propre bus de données, indépendants l’un de l’autre.

A la lumière de tout ce que nous venons de dire, il devrait être clair que si une capture d’image est stoppée, l’on obtient dans tous les cas une image correcte, même si la vitesse d’horloge diffère de beaucoup de celle de l’horloge interne.

Tandis que si l’on travaillait en laissant aller la scrutation (FREEZE à l’état 1), la différence de fréquence et de phase serait perceptible, et on aboutirait à des images composées de morceaux provenant de plusieurs images déclenchées à des moments différents.

La ligne RESET, présente sur le bus d’interface, sert pour que le dispositif qui commande le module digitaliseur puisse effacer la page RAM réservée à la lecture.

La raison en est ici exactement la même que celle que nous venons de détailler à propos de l’écriture, et doit être recherchée dans la façon dont la mémoire fonctionne.

Rappelez-vous que nous utilisons un transfert de type série. L’extraction des signaux, octet après octet, est séquentielle et - par conséquent - au bout de 120000 impulsions il faut remettre à zéro le compteur interne qui adresse la mémoire tampon, pour que la lecture du buffer recommence à partir du début.

Le module digitaliseur

Examinons son étage d’entrée. Cet étage est constitué du transistor T1, un NPN monté en collecteur commun, jouant le double rôle de buffer et de séparateur.

Amplifiant le signal vidéo d’entrée, il évite de surcharger la source.

Une partie du signal est acheminée vers le séparateur des tops de synchro (U1), et une autre partie est acheminée vers le convertisseur A/D (U3) à travers un filtre, constitué par C2, R1, L1 et C4, piégeant les tops de chrominance présents dans les images couleur, lorsque le signal vidéo composite provient d’une caméra couleur ou de la prise péritel d’un magnétoscope couleur.

Le niveau du signal issu de ce filtre, avant d’atteindre l’entrée du convertisseur (broche 8), est réglé - par la résistance ajustable R6 - à un potentiel permettant de référencer le signal vidéo au-dessus de zéro volt (offset), étant donné que celui-ci est normalement négatif.

L’échelle - qui, dans notre cas, est représentée par la largeur de la gamme d’échantillonnage - dépend de la valeur de la tension appliquée sur la broche 9. Ici, elle est de 2,7 volts, obtenue par la diode zener DZ1. Avec cette valeur, l’on obtient des pas d’environ 11 millivolts chacun, soit 11 mV par bit. Comme la conversion se fait sur 8 bits, cela permet bien 256 paliers.

La réalisation pratique

Nous nous devons de signaler que, de par son évidente complexité, la réalisation de ce digitaliseur n’est pas à la portée des débutants, d’autant plus qu’il comporte un certain nombre de CMS, composants petits et délicats.

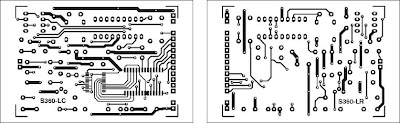

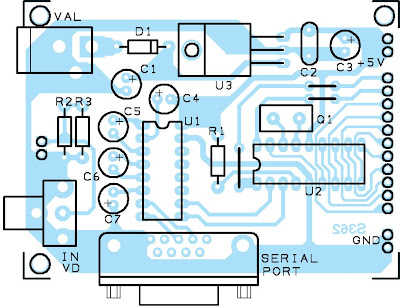

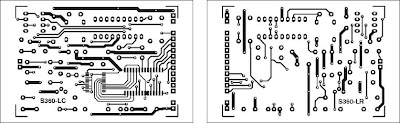

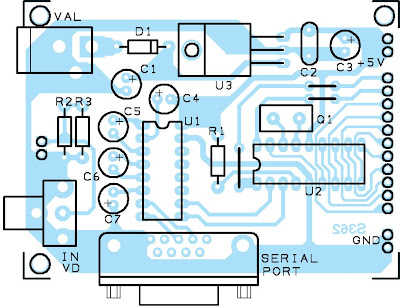

Deux platines sont nécessaires (voir figure 17) : une pour le module digitaliseur proprement dit (figures 9 et 10), et une autre pour le module de contrôle (figures 14 et 15).

Pour le module digitaliseur, nous avons utilisé un circuit imprimé double face à trous métallisés. Si vous réalisez vous-même ce circuit, nous supposons que vous connaissez les règles à mettre en pratique dans ce cas.

Lorsque vous disposez de ce circuit, vous pouvez monter les composants en partant toujours des CMS puis en poursuivant par les plus bas pour terminer par les plus hauts.

Pour réduire les dimensions, plusieurs composants sont d’un modèle pour montage en surface (CMS). Ce type de composant demande une certaine pratique pour être mis en place. Utilisez un fer à souder professionnel, à thermostat, réglé sur 350 °C et maintenez la panne toujours extrêmement propre. Soudez rapidement, sans jamais insister, avec de la soudure 8/10 de mm au plus.

Les circuits intégrés doivent préalablement être centrés pour que chaque broche pose sur sa respective pastille.

Ensuite ils doivent être fixés par deux minuscules points de soudure effectués l’un sur la première broche d’une rangée, l’autre sur la dernière broche de la rangée opposée, de manière à en assurer la tenue mécanique. Après quoi on soudera toutes les autres broches.

Cette méthode, consistant à d’abord s’assurer du bon positionnement du circuit intégré sur les pastilles et ensuite à le bloquer par de minuscules points de soudure effectués sur deux broches diamétralement opposées, évite que le circuit bouge en cours de soudure, et assure les meilleurs résultats.

Pour les autres composants, valent les sempiternelles recommandations: respecter les polarités des condensateurs chimiques, l’orientation des circuits intégrés, etc..

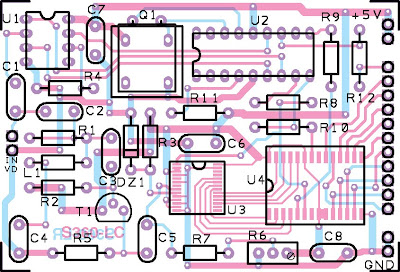

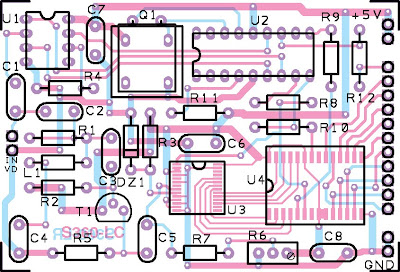

Figure 9 : Schéma d’implantation des composants du digitaliseur.

Figure 9 : Schéma d’implantation des composants du digitaliseur.

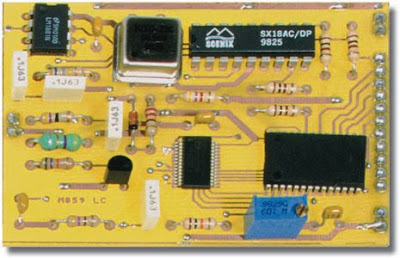

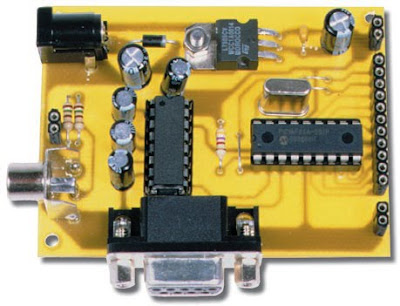

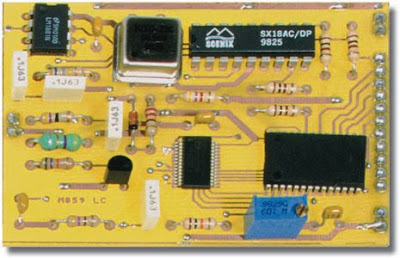

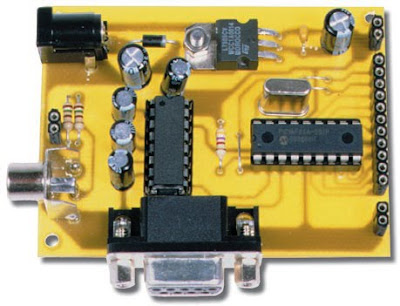

Figure 10 : Photo d’un des prototypes du digitaliseur prêt à l’emploi.

Figure 10 : Photo d’un des prototypes du digitaliseur prêt à l’emploi.

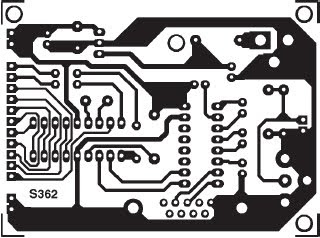

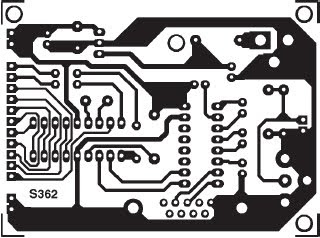

Figure 11 : Dessin, à l’échelle 1, du circuit imprimé double face à trous métallisés du digitaliseur vidéo. Côté pistes (11a) et côté composants (11b).

Figure 11 : Dessin, à l’échelle 1, du circuit imprimé double face à trous métallisés du digitaliseur vidéo. Côté pistes (11a) et côté composants (11b).

Liste des composants du digitaliseur

R1 = 47 Ω

R2 = 56 kΩ

R3 = 220 Ω

R4 = 680 kΩ

R5 = 470 Ω

R6 = 10 kΩ trimmer multitour

R7 = 10 kΩ

R8 = 100 Ω

R9 = 100 Ω

R10 = 100 Ω

R11 = 4,7 kΩ

R12 = 100 Ω

C1 = 100 nF polyester

C2 = 100 nF polyester

C3 = 100 nF polyester

C4 = 100 nF multicouche

C5 = 100 nF polyester

C6 = 100 nF multicouche

C7 = 100 nF multicouche

C8 = 100 nF multicouche

U1 = Intégré LM1881

U2 = μC SX18AC - MF360A

U3 = TDA8761

U4 = μC AL422-MF360B

L1 = Self 4,7 μH

DZ1 = Zener 2,7 V

T1 = NPN BC547B

Q1 = Oscillateur 50 MHz

Divers :

1 Support 2 x 4 broches

1 Support 2 x 9 broches

17 Picots longs en bande sécable pas 2,54

1 Circuit imprimé réf. = S360

Figure 12 : Schéma électrique du module d’interface.

Figure 12 : Schéma électrique du module d’interface.

Figure 13 : Brochage du microcontrôleur PIC 16F84 assurant le contrôle du module d’interface.

Figure 13 : Brochage du microcontrôleur PIC 16F84 assurant le contrôle du module d’interface.

Figure 14 : Schéma d’implantation des composants du module d’interface.

Figure 14 : Schéma d’implantation des composants du module d’interface.

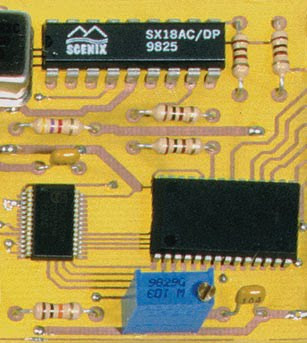

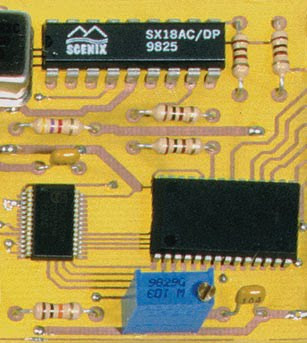

Figure 15 : Photo d’un des prototypes du module d’interface prêt à l’emploi.

Figure 15 : Photo d’un des prototypes du module d’interface prêt à l’emploi.

Figure 16 : Dessin, à l’échelle 1, du circuit imprimé du module d’interface.

Figure 16 : Dessin, à l’échelle 1, du circuit imprimé du module d’interface.

Liste des composants de l’interface

R1 = 4,7 kΩ

R2 = 150 Ω

R3 = 150 Ω

C1 = 100 μF 25 V électrolytique

C2 = 100 nF multicouche

C3 = 100 μF 25 V électrolytique

C4 = 1 μF 63 V électrolytique

C5 = 1 μF 63 V électrolytique

C6 = 1 μF 63 V électrolytique

C7 = 1 μF 63 V électrolytique

D1 = Diode 1N4007

U1 = Intégré MAX232

U2 = μC PIC16F84-20-MF362

U3 = Régulateur 7805

Q1 = Quartz 20 MHz

Divers :

1 Support 2 x 8 broches

1 Support 2 x 9 broches

17 Support en bande sécable pas 2,54

1 Prise alimentation pour ci

1 Prise RCA pour ci

1 Connecteur DB9 mêle pour ci

1 Circuit imprimé réf. = S362

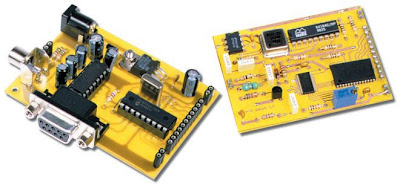

Assemblage des deux modules

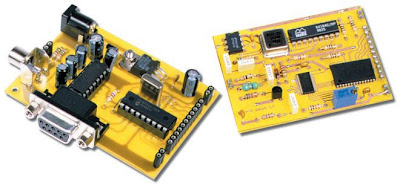

Une fois que le module de contrôle a été assemblé (figures 14 et 15), il faut interconnecter les deux platines, l’une au-dessus de l’autre, comme pour former un sandwich (voir photo en début d’article).

Utiliser pour cela des embases à picots droits, simple rangée, sécables, ou des connecteurs car te à car te, à picots longs d’au moins 20 mm, en regard desquels vous devrez fixer des embases femelles de même diamètre.

Il y a deux liaisons à créer en correspondance de l’arrivée du signal vidéo ;

11 autres liaisons pour les lignes de bus (dont 8 pour les données, une pour le signal d’horloge, une pour le Reset et une pour le FREEZE) et, enfin, deux autres liaisons, situées au prolongement des lignes de bus, portant l’une le +5 volts et l’autre la masse. Il faudra ensuite enficher les deux cartes.

Le montage étant terminé, il ne reste plus qu’à relier le digitaliseur au port série du PC, moyennant un câble pour modem, et installer le logiciel de gestion (voir figure 18) dans le disque dur.

Figure 17: Les deux platines se montent l’une au-dessus de l’autre, comme pour former un sandwich. Utilisez d’un côté des picots droits, longs au moins 20 mm, et de l’autre des embases femelles adaptées, ou des supports tulipe.

Figure 17: Les deux platines se montent l’une au-dessus de l’autre, comme pour former un sandwich. Utilisez d’un côté des picots droits, longs au moins 20 mm, et de l’autre des embases femelles adaptées, ou des supports tulipe.

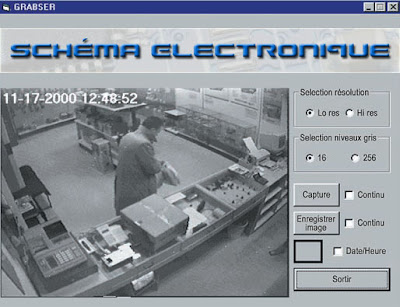

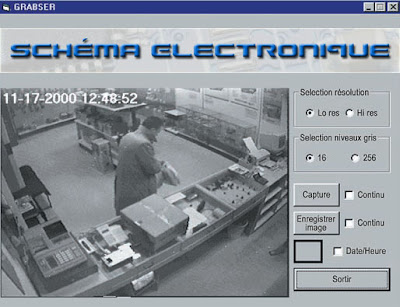

Le logiciel qui gère ce digitaliseur s’appelle GRABSER

Figure 18 : Le logiciel de gestion.

Figure 18 : Le logiciel de gestion.

L’interface graphique qui s’ouvre après l’avoir lancée, est constituée de deux parties : d’un côté (la plus grande partie de l’écran) l’image fournie par le digitaliseur, et - de l’autre - des boutons et des cases à cocher.

Dans cette partie, du haut en bas, on trouve la zone correspondant au choix de la résolution (faible ou haute), puis celle correspondant au choix des niveaux de gris (16 ou 256), ensuite, celles concernant le mode de capture et de mise en mémoire, avec possibilité d’incruster le jour et l’heure.

Puis, enfin, le bouton qui permet de sortir du programme. Voyons ces commandes, l’une après l’autre.

Lo re fournit une résolution de 200 x 150 points. Hi re fournit une résolution de 400 x 300 points.

Dans la zone correspondant au choix des tons de gris : “16” fournit des images à 16 niveaux de gris, tandis que “256” fournit des images à 256 niveaux de gris. Même si nous ne vous avions rien dit à leur sujet, vous l’auriez deviné, tant l’interface est claire pour ce qui concerne ces deux premières zones.

Venons-en au bouton “Capture”.

Lorsqu’on clique sur ce bouton, le PC demande au module de lui envoyer la dernière image saisie.

Le module principal active alors la ligne FREEZE, et le microcontrôleur (SCENIX) du digitaliseur complète la numérisation de la dernière image qu’il a en cours de traitement et l’envoie au PIC à la vitesse déterminée par les résolutions demandées par l’utilisateur.

Le microcontrôleur élabore les données en tenant compte de tout ce qui lui a été demandé (niveaux de gris) et les transmet en série au PC. Dans cette phase, le nombre des niveaux de gris est déterminant quant à la vitesse de communication et, par conséquent, à l’intervalle séparant deux images successives.

Si l’on a demandé une image à 16 niveaux de gris, le PIC envoie deux pixels par image.

En cliquant sur “Continu” à côté de la touche “Capture”, on demande une numérisation cyclique ; le système mémorise alors les images en continu et met cycliquement à jour l’écran vir tuel. Lorsque ce mode de fonctionnement a été choisi, un voyant carré passe au rouge pendant tout le temps nécessaire à la digitalisation de l’image en cours, et passe au ver t à la fin de chaque prise de vue.

La touche “Enregistrer image” permet d’enregistrer l’image présente à l’écran sur le disque dur.

La mémorisation se fait dans le dossier sous le nom duquel le logiciel a été installé, en format bitmap ; donc : avec l’extension .bmp.

En cliquant sur “Continu” à côté de la touche “Enregistrer image” on mémorise sur le disque dur toutes les images en suivant, toujours au format bitmap.

Pour les différencier l’une de l’autre, le logiciel leur attribue à chacune la date et l’heure du moment de la capture.

Enfin, la touche “Date/Heure” provoque l’incrustation de la date et de l’heure dans l’image (paramètres se référant, évidemment, à l’horloge de la carte mère) comme on peut le voir, en haut à gauche, sur l’illustration.

Il n’est pas nécessaire de préciser que l’électronique est en continuelle évolution dans tous les domaines.

Scanner, webcam, ou grabber ?

Un secteur d’application extrêmement intéressant est celui qui concerne l’acquisition et le traitement d’images, et plus particulièrement les signaux vidéo, eu égard à la croissante nécessité de faire aujourd’hui avec l’ordinateur ce qu’autrefois se faisait avec les appareils photo, les chambres noires et les pellicules argentiques.

Une fois disponible sous forme de “bits”, l’image peut être “traitée”, c’est-à-dire utilisée pour faire de tout.

Par exemple : elle peut être retouchée, superposée à une autre, modifiée, envoyée par voie télématique, et subir un tas d’autres traitements.

Le but des “digitaliseurs” consiste à convertir une image analogique en format numérique. Autrement dit : à la présenter sous forme de bits.

Les systèmes d’acquisition d’images sont nombreux et différents les uns des autres en fonction de ce à quoi ils doivent servir.

S’il s’agit, par exemple, de saisir une photo en ordinateur, le plus simple est de faire appel à un scanner.

Si l’on veut saisir des images, ce n’est plus au scanner qu’il convient de faire appel, mais plutôt à une webcam, ou à un appareil photo numérique.

Si, par contre, l’application demande de capturer un photogramme, ou les images d’un film issues d’une caméra ou d’un magnétoscope, alors, les appareils qui conviennent ne sont plus, ni le scanner, ni la webcam, ni l’appareil photo numérique.

Ce qu’il faut dans ces cas, est le “grabber”.

Qu’est-ce qu’un “grabber” ?

Pratiquement, il s’agit d’un appareil capable de capturer (to grab) et de mémoriser le signal vidéo composite provenant d’une caméra télé, de décomposer chaque photogramme (frame), et de porter l’image à l’écran.

Vue l’énorme potentialité d’un tel appareil, nous avons pensé mettre au point un système d’acquisition d’images pour PC, relativement simple, qui ouvrira la route à une série de projets du même style, liés au monde de la sécurité et de la surveillance, tous innovants.

En fait, l’analyseur vidéo par lequel nous commençons et que nous vous présentons ce mois-ci, est formé - à plus proprement parler - de deux sous-ensembles : un “grabber” et un module d’interface aux normes RS232-C assurant la liaison au port série du PC (figure 1).

Le grabber est néanmoins le coeur de l’appareil.

Il s’agit de l’élément qui capture le signal vidéo, l’échantillonne, et stocke en mémoire vive (RAM adaptée) un photogramme à la fois, c’est-à-dire chaque frame (image instantanée) d’une prise de vue.

Ce module s’occupe du déroulement de toutes les opérations, mémorise, et extrait de la RAM les données sur 8 bits en parallèle.

En association à cet ensemble, il y en a un autre, que nous appelons “unité de contrôle”, qui dialogue avec le “grabber” par son bus, et accomplie différentes fonctions.

Il s’occupe de l’acquisition du signal vidéo composite, balaye (moyennant un signal d’horloge que lui-même génère) les données de la mémoire, les extrait, et convertit les informations ainsi obtenues en format série, c’est-à-dire en impulsions qu’il envoie au PC auquel il est relié et dont il reçoit, tour à tour, les commandes relatives à ce qu’il doit faire.

Le tout, sous contrôle d’un logiciel écrit pour fonctionner en environnement Windows 95/98, comportant une interface visuelle constituée, en grande partie, par un écran virtuel dans lequel apparaissent les images mémorisées, à savoir : les images capturées.

Sur l’interface visuelle, il existe des boutons et des cases à cocher, un pour chaque tâche que l’on veut accomplir : capturer une image passant à l’écran à un moment donné, la mémoriser (en format bitmap), sortir du programme… ou encore : choisir la résolution de l’image (élevée ou faible), sélectionner les tons de gris, incruster dans l’image la date et l’heure.

Celui que nous avons appelé le coeur du circuit (le “grabber”), à savoir le module assurant la capture vidéo, nous le retrouverons dans d’autres projets, que nous préparons pour les présenter à l’avenir, adaptés à d’autres usages.

Commençons donc par voir comment celui-ci fonctionne, et remettons à plus tard l’examen de l’interface et du logiciel de gestion.

Le “grabber”

Le grabber, autrement dit le sousensemble qui effectue la digitalisation, dont le schéma électrique est visible en figure 2 et le schéma synoptique en figure 3, se présente sous la forme d’une carte (voir figures 9 et 10) pourvue de 15 points de contact, destinés à s’interconnecter à l’unité de contrôle (voir figures 14 et 15) et de deux points de contact constituant l’entrée du signal vidéo.

En gros, il échantillonne la grandeur présente sur son entrée, mémorise les données relatives à chaque pixel dans une RAM spéciale (voir figure 4) puis active une mémoire tampon dont la capacité permet de contenir un photogramme entier, de sorte à permettre au module d’interface d’y venir chercher les données, pour les décharger à son rythme vers le PC.

L’échantillonnage est effectué par un convertisseur A/D à 8 bits (voir figure 5).

Tout le module est géré par un microcontrôleur haut de gamme, à savoir un SCENIX SX18 (voir figure 6), capable de travailler à une fréquence d’horloge de 50 MHz, issue d’un résonateur DIL intégré (référencé Q1 dans le schéma) et arrivant sur la broche 5.

Le rôle de ce microcontrôleur est très important.

Il génère, entre autres, le signal d’horloge au rythme duquel le convertisseur A/D effectue les échantillonnages, et synchronise - sur ce même rythme - la mise en mémoire d’une image dans la portion de RAM réservée à l’écriture.

En effet, le signal servant d’horloge au convertisseur, qui correspond au WCK (Write ClocK), cadence, au même rythme, le convertisseur A/D (broche 1 de U3) et la mémoire (broche 6 de U4).

Figure 1 : Une autre vue d’un des prototypes prêt à fonctionner.

Figure 1 : Une autre vue d’un des prototypes prêt à fonctionner.Une RAM à deux “pages”

Un autre rôle important du microcontrôleur est la gestion du partage de la RAM en deux “pages”, c’est-à-dire en deux blocs virtuels : un dans lequel le convertisseur analogique/digital écrit les octets correspondant à chaque pixel et l’autre dans lequel l’interface de sortie (représentée par la deuxième carte) peut lire à tout moment, soit en temps réel, soit lors de l’arrêt d’une acquisition (commandée au moyen de la ligne FREEZE du bus).

Ceci explique (voir figure 4) pourquoi la mémoire (une AL422 fabriquée par la société AVER LOGIC) dispose de commandes en double, dont deux lignes d’horloge séparées (une pour l’écriture, appelée WCK = Write ClocK, et une pour la lecture, appelée RCK = Read ClocK), et deux lignes de Reset séparées (une ligne de Reset pour l’écriture, appelée WRST = Write ReSeT, et une ligne de Reset pour la lecture, appelée RRST = Read ReSeT).

Le module d’interface

Le module d’interface consiste en une carte qui s’interconnecte avec le module digitaliseur au moyen de picots enfichables. Par ce biais, les deux modules se partagent non seulement les lignes d’alimentation, mais aussi le bus de données, les lignes de Reset, le signal d’horloge de la RAM U4, et celui du FREEZE du SCENIX.

Il est entièrement ramassé autour du microcontrôleur PIC 16F84, auquel s’ajoute juste un convertisseur TTL/RS232 bidirectionnel pour communiquer avec le PC par le port série.

Il suffit de regarder son schéma électrique pour en constater l’extrême simplicité.

Le microcontrôleur en est le coeur.

Celui-ci est exploité au plein de ses capacités, car toutes les lignes de port sont utilisées : les 8 lignes du port B (B0, B1, B2, B3, B4, B5, B6 et B7), initialisées en entrées, constituent le bus par lequel il lit les données, autrement dit, la voie par laquelle il prélève, octet après octet, les images digitalisées par le convertisseur A/D.

Du côté du port A, deux lignes servent à la liaison série, tandis qu’A0, A1 et A2 sont configurées en sorties et servent à contrôler les lignes FREEZE, Clock et Reset de la partie lecture de la RAM à deux pages.

L’alimentation de l’ensemble des circuits est obtenue en stabilisant à 5 volts la tension continue portée sur le connecteur VAL. La diode D1 protège contre les risques d’inversion de polarités.

Pour obtenir les 5 volts stabilisés, on fait appel à un classique 7805.

Les condensateurs qui l’entourent, filtrent l’alimentation d’éventuels signaux parasites pouvant provenir de l’extérieur, et surtout des transitoires générées tout particulièrement par le module digitaliseur, lequel travaille à des fréquences très élevées. U1 assure l’interface avec le PC. Il met en oeuvre un MAX232 qui rend compatibles les signaux du port série, fournis au standard RS232-C (impulsions variant entre +12 volts et –12 volts), à ceux utilisés par les différents circuits logiques (0-5 volts) et par les microcontrôleurs, dans les échanges qui ont lieu entre le PC et les modules, et inversement.

La communication série se fait à la vitesse de 57 600 bps (bits par seconde), ce qui suppose que le PC à utiliser doit disposer d’un UART (Universal Asynchronous Receiver Transmitter) convertisseur série/parallèle et parallèle/série, rapide (16550 compatible, ou supérieur).

Mais voyons ce qui ce passe exactement dans le circuit à partir du moment où il est mis sous tension.

Figure 2 : Schéma électrique du module digitaliseur.

Figure 2 : Schéma électrique du module digitaliseur.Synoptique complet du digitaliseur

Voulant résumer, on peut dire que le microcontrôleur du module d’interface (un PIC 16F84) interroge cycliquement le bus de sortie du digitaliseur, arrête le balayage après l’exploration complète d’une image, et décharge ensuite les données mémorisées jusque-là.

Mais, procédons en ordre, et voyons plus en détail ce que ce module fait exactement.

Lorsque, à la demande du PC, le microcontrôleur du module d’interface doit transmettre une image digitalisée, il met à l’état bas la ligne aboutissant au FREEZE.

Ainsi faisant, le PIC demande au microcontrôleur du module digitaliseur (le SCENIX) de s’arrêter au terme du balayage du photogramme en cours de transmission.

Le pas suivant est celui qui concerne la génération du signal d’horloge cadençant l’extraction des octets qui sont en fait la mémorisation de l’état de chaque pixel de l’image.

Mais, avant cela, pour être sûrs que l’image soit extraite correctement, le PIC déclenche un Reset sur la ligne de bus aboutissant au RSTR, lequel remet à zéro le compteur d’adresses de la RAM U4 implantée sur le module digitaliseur.

Puis, à chaque impulsion d’horloge, il lit l’octet correspondant, le convertit en format série, lui ajoute les bits de start et de stop (pas celui de parité, car la communication avec le PC a lieu sans contrôle de parité), et l’envoie à l’RXD de la porte RS232-C du PC, où il est lu et traité par un logiciel tournant sous Windows.

Une fois que tous les 120000 octets ont été balayés, on remet à 1 la ligne FREEZE et on bloque l’horloge.

A partir de là, le digitaliseur reprend à mémoriser le signal vidéo.

Le programme de gestion permet de choisir entre une résolution faible et une élevée (voir figure S).

En terme de pixels, la faible résolution correspond à des images en format 200 x 150 points, tandis que la haute résolution correspond à des images en format 400 x 300 points.

Lorsqu’on a opté pour des images à faible résolution, la fréquence d’horloge que le PIC envoie à la mémoire est divisée par quatre, par rapport à la fréquence nominale, car - dans ce cas - seulement un quart des points constitutifs d’une image sont à lire.

L’image envoyée au PC, octet après octet, est alors sensiblement plus petite. Mais, pour éviter de restituer à l’écran une image en petit format, le logiciel effectue un “resizing”.

Cela remet l’image au bon format, en tenant compte évidemment du facteur de division demandé, lequel n’est rien d’autre que le taux choisi pour la résolution.

Quant à la sélection des tons de gris, elle aussi se fait au moyen de l’interface graphique.

Cela revient à indiquer le nombre de bits que l’on veut utiliser pour la mémorisation des pixels.

En sachant que le convertisseur A/D numérise chaque point d’image avec une définition de 8 bits, il en résulte une échelle de 256 niveaux de gris possibles.

Si l’utilisateur choisit une résolution à 256 niveaux, les données sont transformées au rythme d’un octet par pixel ; tandis que s’il choisit seulement 16 niveaux, une sorte de compression est opérée qui conduit le digitaliseur à numériser sur seulement 4 bits.

A ce point, faisons les comptes : le temps nécessaire au PC pour reconstituer une image à faible résolution (200 x 150 pixels) avec seulement 16 niveaux de gris, est d’environ 7 secondes ; tandis que pour reconstituer une image en résolution 400 x 300 pixels avec le même nombre de niveaux de gris, le PC a besoin de 20 secondes.

Considérons maintenant le cas d’une image toujours en définition 200 x 150 points, mais avec 256 niveaux de gris : le PC a besoin de 12 secondes, et pour reconstituer une image à la plus haute résolution et avec le maximum de niveaux de gris (256), il lui faut 35 secondes.

Le module vidéo

Figure 3: Le module vidéo, schéma synoptique (3a) et photo d’un prototype terminé (3b).

Le “grabber”, véritable coeur de l’appareil, est l’élément qui digitalise le signal vidéo.

Il se présente sous la forme d’une carte pourvue de 15 points de contact destinés à s’interconnecter à d’autres unités de contrôle, et de deux points de contact destinés à recevoir le signal vidéo.

Brièvement présenté, les tâches qui lui sont dévolues se résument ainsi : il échantillonne la grandeur présente sur son entrée, mémorise dans une RAM spéciale les données relatives à chaque pixel, puis active une mémoire tampon (contenant un photogramme complet) d’où l’on peut ensuite extraire les données en forme série.

L’échantillonnage est effectué par un convertisseur A/D à 8 bits, qui stocke les données dans une RAM de 3 Mo.

Toutes les opérations s’effectuent sous le contrôle d’un microcontrôleur SCENIX SX18 travaillant à 50 MHz.

La RAM vidéo

Figure 4 : La RAM vidéo.

Figure 4 : La RAM vidéo.Les données échantillonnées par le convertisseur A/D sont stockées dans une DRAM (RAM dynamique) AL422 de 3 mégabits en format 384 K x 8 bits, fabriquée par AVER LOGIC.

La particularité de cette RAM, outre son extrême rapidité (temps d’accès inférieur à 15 ns), est de posséder pas mal de choses en double: deux lignes d’horloge séparées: une pour l’écriture (WCK = Write ClocK) et une pour la lecture (RCK = Read ClocK) ; deux lignes de Reset séparées : WRST (Write ReSeT) et RRST (Read ReSeT) ; et enfin deux bus de données séparés, chacun de 8 bits : un bus pour les données qui entrent, et un autre pour les données qui sortent.

Le buffer de la mémoire (celui qui stocke les données relatives à chaque image) est du type FIFO (First In, First Out) capable de contenir 819 x 480 bytes.

Le convertisseur AD pour signaux vidéo

Figure 5: Le convertisseur AD pour signaux vidéo.

Le schéma synoptique est donné en figure 5a, le rôle de chaque broche en 5b et le brochage lui-même en 5c.

Ce convertisseur a un rôle de tout premier plan dans notre application. Il s’agit d’un conver tisseur à 9 bits TDA8761 fabriqué par Philips, dont - pour raisons de compatibilité - nous n’en utilisons que 8.

Devant échantillonner un signal vidéo composite, dont la largeur de bande est typiquement de 5,5 MHz, il travaille à la fréquence de 40 MHz.

A l’intérieur de ce circuit on trouve un convertisseur à mailles R/2R, un latch contenant les données échantillonnées et successivement transférées dans le buffer de sor tie, un clock et les nécessaires circuits relatifs à la logique de contrôle.

La conversion démarre en présence d’une impulsion positive sur la broche 1 (CLK).

Les données en format 8 bits, issues de l’échantillonnage de la grandeur lue à l’entrée (broche 8, VI), passent dans le latch, puis d’ici dans le buffer CMOS (toujours actif, car nous avons relié la broche 10 Output Enable à la masse), et enfin sortent par les broches 17 à 25.

Le microcontrôleur SCENIX SX18

Figure 6: Le microcontrôleur SCENIX

Structure interne (6a) et brochage (6b) du microcontrôleur SCENIX SX18AC/DP en boîtier DIP18. Ce type de microcontrôleur peut travailler à une vitesse d’horloge pouvant aller jusqu’à 50 MHz.

Figure 7 : Le séparateur de tops synchro.

Figure 7 : Le séparateur de tops synchro.Pour cadencer le microcontrôleur SCENIX à la vitesse du signal vidéo composite présent à l’entrée du module d’acquisition, nous avons extrait les tops de ligne et de trame d’un circuit expressément étudié pour. Il s’agit du LM1881 de National Semiconductor, équivalent au EL4581 de ELANTEC, dans lequel, de précis circuits à seuil opèrent les filtrages nécessaires et fournissent les signaux primaires séparément.

Analyse du circuit

Le microcontrôleur commence par initialiser ses lignes d’entrée/sortie. Les lignes de port B0 et B1 sont configurées comme entrées, car c’est sur ces lignes que vont arriver les tops de ligne et de trame provenant de U1 (voir figure 7).

Les lignes B2, B3 et B4 sont configurées comme sorties ; elles sont destinées - respectivement - l’une à fournir le signal d’horloge (PIXCLK) qui synchronise la RAM et le convertisseur A/D, l’autre à gérer le Reset de la section mémoire destinée à l’écriture (le Reset de la “page” lecture est contrôlé par le bus…), et l’autre à commander la broche R/W de la RAM. La ligne B6 est configurée en entrée : elle lit la commande FREEZE provenant du module d’interface, commande que nous décrirons plus en avant. Enfin, la ligne B6, configurée elle aussi en entrée, reçoit les impulsions de la broche 7 (ODD/EVEN) de U1.

Le microcontrôleur est alimenté par les broches 14 (+5 volts) et 5 (masse), et travaille au rythme du signal d’horloge que le résonateur intégré lui envoie sur la broche 16.

Après la phase d’initialisation, il se synchronise avec les tops de trame et de ligne contenus dans le signal vidéo composite arrivant sur l’entrée (IN VIDEO) et que le séparateur de tops de synchronisations U1 extrait.

Ainsi scindés, ces deux signaux servent à reconstituer la trame de l’image initiale, à laquelle, cependant, on retire un certain nombre de lignes, dans le but de réduire la quantité de mémoire nécessaire à stocker chaque photogramme.

Plus exactement, le top de synchronisation de trame est utilisé pour le rafraîchissement de la mémoire et pour signaler au microcontrôleur à quel moment précis se termine l’acquisition d’un photogramme, tandis que le top de synchro ligne ser t à cadencer le convertisseur A/D et la mémoire, car il renseigne du moment auquel chaque ligne commence et finit.

Autrement dit : le microcontrôleur récupère - à partir du balayage horizontal - le pixel-clock (PIXCLK) qu’il envoie à la fois sur le convertisseur A/D et sur la partie RAM réservée à l’écriture (WCK), et - à partir du balayage vertical - l’information lui indiquant précisément à quel moment se termine l’écriture d’un photogramme dans la RAM.

C’est cette dernière information qui permet notamment la suppression des balayages de retour (flyback) qu’il n’aurait aucun sens de mémoriser.

Ainsi que nous l’avons laissé entendre plus haut, étant donné qu’il faut composer avec l’espace mémoire disponible, certaines lignes sont retirées de l’image, de sorte à limiter chaque photogramme au format max de 400 x 300 pixels (400 pixels en horizontale et 300 pixels en ver ticale). Ce qui conduit à une définition totale de 120 000 pixels.

Chaque pixel, ou point élémentaire d’image, est mémorisé à une fréquence de ligne d’environ 5 MHz. Et comme cette même fréquence, synthétisée par U2, cadence aussi les pas de la conversion A/D, la parfaite synchronisation entre celle-ci et celle du signal vidéo, garantit que la capture et la mémorisation en RAM des pixels de chaque ligne commence exactement au moment où celles-ci prennent naissance.

Puisque le clock qui pilote le convertisseur A/D agit aussi sur l’entrée WCK, les informations échantillonnées sont transférées dans la portion de RAM destinée à l’écriture, au même rythme et en parfaite correspondance.

Voyons plus en détail comment vont les choses.

Au démarrage d’une trame, le séparateur de tops synchro fournit au microcontrôleur une impulsion que celui-ci utilise pour effacer la mémoire (via WRST) et pour commencer à compter les cases mémoire, à partir de la case zéro.

Pendant ce temps-là, U3 est inopérant, jusqu’à ce que le microcontrôleur lui envoie une impulsion d’horloge, obtenue par U1, par extraction du top départ de la synchro horizontale contenu dans le signal vidéo composite.

A l’arrivée de cette impulsion, le convertisseur A/D lit le signal qui arrive sur son entrée (broche 3) et, au moment opportun (moment déterminé par le microcontrôleur, c’est-à-dire juste après le balayage de retour, que nous avons nommé flyback) échantillonne le niveau analogique correspondant au premier pixel, et le convertit en format digital sur 8 bits. Il s’ensuit un octet aussitôt écrit en RAM, car le même signal d’horloge qui incrémente la conversion A/D, incrémente aussi, en même temps, les adresses de la RAM. C’est ainsi que l’octet contenant l’information relative au premier pixel de la première ligne est écrit dans la première case mémoire.

Puis arrive la deuxième impulsion : le convertisseur l’échantillonne et envoie en RAM l’octet relatif au deuxième pixel.

Puis, à la troisième impulsion, il fait de même avec le troisième octet… et ainsi de suite, jusqu’au 400e.

A ce moment, la première ligne a été échantillonnée et mémorisée. On passe à la ligne suivante.

Une fois que les 300 lignes constituant une page écran entière sont passées, les 120 000 cases RAM ont été remplies: une case par pixel.

Un photogramme complet a ainsi été mémorisé.

C’est alors qu’un nouveau top de synchronisation verticale arrive au microcontrôleur. Celui-ci envoie un Reset à la RAM, de sorte que les nouvelles données que le convertisseur A/D enverra en mémoire à partir de maintenant, soient écrites à partir de la première case mémoire, et se réfèrent à une nouvelle image.

Recommence ainsi un nouveau cycle : le convertisseur digitalise un pixel et envoie un (nouveau) premier octet, qui est stocké dans la case mémoire 1, etc.

Les nouvelles données écrasent les précédentes, dont elles prennent la place, après que le Reset ait fait table rase de ce que la RAM contenait précédemment.

Toute nouvelle ligne de l’image successive remplace le contenu de l’image précédente. Ce détail est important, car il détermine le résultat que l’utilisateur peut obtenir ; résultat qui dépend de la façon dont on lit le buffer.

Si la lecture est demandée en temps réel, le système restitue une série d’informations reconstituant exactement la page écran mémorisée.

Si par contre la lecture est plus lente que la mémorisation, les données que le buffer délivre ne correspondent pas à une entière séquence de digitalisation.

Pour cette raison il peut être utile de se servir de l’option arrêt sur image.

Dans ce cas, c’est la fin d’un photogramme qui déclenche le vidage du buffer.

Les informations que celui-ci contient sont alors mises sur le bus de données (indiquées par DATA sur le schéma) et le module d’interface, dont le schéma électrique est donné en figure 12, peut élaborer des signaux (voir figure 18) qui, portés à l’écran, restituent l’image capturée au moment voulu.

Conclusion : pour éviter de déclencher des lectures trop hâtivement, il convient de gérer avec discernement la ligne FREEZE.

Normalement, cette ligne doit être maintenue à l’état haut.

Si elle est mise à zéro, le microcontrôleur arrête toute scrutation, bloque le pixelclock, et - par voie de conséquence - l’écriture en RAM de toute nouvelle donnée.

Le microcontrôleur prend ensuite le contenu des 120000 adresses contenant le photogramme et le transfère dans la page de sortie de la RAM, d’où le module d’interface, sous le contrôle du microcontrôleur PIC16F84 (voir figure 13), peut le saisir via le bus de données, au rythme d’une horloge indépendante.

Figure 8: Vue sur le microcontrôleur SX18 et sur la RAM vidéo AL422.

Figure 8: Vue sur le microcontrôleur SX18 et sur la RAM vidéo AL422.Images cohérentes

Il convient de préciser que lorsque la ligne FREEZE est portée au niveau bas, l’acquisition ne s’arrête pas inconditionnellement, car sinon l’interface déverserait sur le bus non pas des données se rappor tant à une unique image, mais des données restituant des morceaux d’images mélangées.

On aurait à l’écran une image composée en partie par des lignes provenant de la mise en mémoire de l’image précédente, et - pour une autre partie - de lignes provenant de l’image dont la capture était en cours d’acquisition avant l’arrêt forcé.

C’est pourquoi, le microcontrôleur va toujours jusqu’au bout dans la digitalisation d’une image, et n’arrête le convertisseur A/D et l’incrémentation de la RAM qu’après avoir mémorisé tous les pixels d’une image, et c’est seulement au terme de cette procédure qu’il met au repos la ligne du pixelclock.

Ainsi faisant, on a la certitude que les données extraites par U4 se rapportent toutes à la même image.

Lorsqu’on parle d’horloge, au cours d’une opération d’écriture en mémoire, l’on se réfère au signal que l’interface fait parvenir à la broche 20 de la RAM.

Autrement dit, à la ligne CLOCK du bus.

C’est à ce point que nous pouvons revenir sur ce à quoi nous avions fait allusion plus haut ; à savoir : la totale indépendance entre les deux pages de la RAM: celle d’écriture, et celle de lecture, pourvues - chacune - de son propre clock et de son propre bus de données, indépendants l’un de l’autre.

A la lumière de tout ce que nous venons de dire, il devrait être clair que si une capture d’image est stoppée, l’on obtient dans tous les cas une image correcte, même si la vitesse d’horloge diffère de beaucoup de celle de l’horloge interne.

Tandis que si l’on travaillait en laissant aller la scrutation (FREEZE à l’état 1), la différence de fréquence et de phase serait perceptible, et on aboutirait à des images composées de morceaux provenant de plusieurs images déclenchées à des moments différents.

La ligne RESET, présente sur le bus d’interface, sert pour que le dispositif qui commande le module digitaliseur puisse effacer la page RAM réservée à la lecture.

La raison en est ici exactement la même que celle que nous venons de détailler à propos de l’écriture, et doit être recherchée dans la façon dont la mémoire fonctionne.

Rappelez-vous que nous utilisons un transfert de type série. L’extraction des signaux, octet après octet, est séquentielle et - par conséquent - au bout de 120000 impulsions il faut remettre à zéro le compteur interne qui adresse la mémoire tampon, pour que la lecture du buffer recommence à partir du début.

Le module digitaliseur

Examinons son étage d’entrée. Cet étage est constitué du transistor T1, un NPN monté en collecteur commun, jouant le double rôle de buffer et de séparateur.

Amplifiant le signal vidéo d’entrée, il évite de surcharger la source.

Une partie du signal est acheminée vers le séparateur des tops de synchro (U1), et une autre partie est acheminée vers le convertisseur A/D (U3) à travers un filtre, constitué par C2, R1, L1 et C4, piégeant les tops de chrominance présents dans les images couleur, lorsque le signal vidéo composite provient d’une caméra couleur ou de la prise péritel d’un magnétoscope couleur.

Le niveau du signal issu de ce filtre, avant d’atteindre l’entrée du convertisseur (broche 8), est réglé - par la résistance ajustable R6 - à un potentiel permettant de référencer le signal vidéo au-dessus de zéro volt (offset), étant donné que celui-ci est normalement négatif.

L’échelle - qui, dans notre cas, est représentée par la largeur de la gamme d’échantillonnage - dépend de la valeur de la tension appliquée sur la broche 9. Ici, elle est de 2,7 volts, obtenue par la diode zener DZ1. Avec cette valeur, l’on obtient des pas d’environ 11 millivolts chacun, soit 11 mV par bit. Comme la conversion se fait sur 8 bits, cela permet bien 256 paliers.

La réalisation pratique

Nous nous devons de signaler que, de par son évidente complexité, la réalisation de ce digitaliseur n’est pas à la portée des débutants, d’autant plus qu’il comporte un certain nombre de CMS, composants petits et délicats.

Deux platines sont nécessaires (voir figure 17) : une pour le module digitaliseur proprement dit (figures 9 et 10), et une autre pour le module de contrôle (figures 14 et 15).

Pour le module digitaliseur, nous avons utilisé un circuit imprimé double face à trous métallisés. Si vous réalisez vous-même ce circuit, nous supposons que vous connaissez les règles à mettre en pratique dans ce cas.

Lorsque vous disposez de ce circuit, vous pouvez monter les composants en partant toujours des CMS puis en poursuivant par les plus bas pour terminer par les plus hauts.

Pour réduire les dimensions, plusieurs composants sont d’un modèle pour montage en surface (CMS). Ce type de composant demande une certaine pratique pour être mis en place. Utilisez un fer à souder professionnel, à thermostat, réglé sur 350 °C et maintenez la panne toujours extrêmement propre. Soudez rapidement, sans jamais insister, avec de la soudure 8/10 de mm au plus.

Les circuits intégrés doivent préalablement être centrés pour que chaque broche pose sur sa respective pastille.

Ensuite ils doivent être fixés par deux minuscules points de soudure effectués l’un sur la première broche d’une rangée, l’autre sur la dernière broche de la rangée opposée, de manière à en assurer la tenue mécanique. Après quoi on soudera toutes les autres broches.

Cette méthode, consistant à d’abord s’assurer du bon positionnement du circuit intégré sur les pastilles et ensuite à le bloquer par de minuscules points de soudure effectués sur deux broches diamétralement opposées, évite que le circuit bouge en cours de soudure, et assure les meilleurs résultats.

Pour les autres composants, valent les sempiternelles recommandations: respecter les polarités des condensateurs chimiques, l’orientation des circuits intégrés, etc..

Figure 9 : Schéma d’implantation des composants du digitaliseur.

Figure 9 : Schéma d’implantation des composants du digitaliseur. Figure 10 : Photo d’un des prototypes du digitaliseur prêt à l’emploi.

Figure 10 : Photo d’un des prototypes du digitaliseur prêt à l’emploi. Figure 11 : Dessin, à l’échelle 1, du circuit imprimé double face à trous métallisés du digitaliseur vidéo. Côté pistes (11a) et côté composants (11b).

Figure 11 : Dessin, à l’échelle 1, du circuit imprimé double face à trous métallisés du digitaliseur vidéo. Côté pistes (11a) et côté composants (11b).Liste des composants du digitaliseur

R1 = 47 Ω

R2 = 56 kΩ

R3 = 220 Ω

R4 = 680 kΩ

R5 = 470 Ω

R6 = 10 kΩ trimmer multitour

R7 = 10 kΩ

R8 = 100 Ω

R9 = 100 Ω

R10 = 100 Ω

R11 = 4,7 kΩ

R12 = 100 Ω

C1 = 100 nF polyester

C2 = 100 nF polyester

C3 = 100 nF polyester

C4 = 100 nF multicouche

C5 = 100 nF polyester

C6 = 100 nF multicouche

C7 = 100 nF multicouche

C8 = 100 nF multicouche

U1 = Intégré LM1881

U2 = μC SX18AC - MF360A

U3 = TDA8761

U4 = μC AL422-MF360B

L1 = Self 4,7 μH

DZ1 = Zener 2,7 V

T1 = NPN BC547B

Q1 = Oscillateur 50 MHz

Divers :

1 Support 2 x 4 broches

1 Support 2 x 9 broches

17 Picots longs en bande sécable pas 2,54

1 Circuit imprimé réf. = S360

Figure 12 : Schéma électrique du module d’interface.

Figure 12 : Schéma électrique du module d’interface. Figure 13 : Brochage du microcontrôleur PIC 16F84 assurant le contrôle du module d’interface.

Figure 13 : Brochage du microcontrôleur PIC 16F84 assurant le contrôle du module d’interface. Figure 14 : Schéma d’implantation des composants du module d’interface.

Figure 14 : Schéma d’implantation des composants du module d’interface. Figure 15 : Photo d’un des prototypes du module d’interface prêt à l’emploi.

Figure 15 : Photo d’un des prototypes du module d’interface prêt à l’emploi. Figure 16 : Dessin, à l’échelle 1, du circuit imprimé du module d’interface.

Figure 16 : Dessin, à l’échelle 1, du circuit imprimé du module d’interface.Liste des composants de l’interface

R1 = 4,7 kΩ

R2 = 150 Ω

R3 = 150 Ω

C1 = 100 μF 25 V électrolytique

C2 = 100 nF multicouche

C3 = 100 μF 25 V électrolytique

C4 = 1 μF 63 V électrolytique

C5 = 1 μF 63 V électrolytique

C6 = 1 μF 63 V électrolytique

C7 = 1 μF 63 V électrolytique

D1 = Diode 1N4007

U1 = Intégré MAX232

U2 = μC PIC16F84-20-MF362

U3 = Régulateur 7805

Q1 = Quartz 20 MHz

Divers :

1 Support 2 x 8 broches

1 Support 2 x 9 broches

17 Support en bande sécable pas 2,54

1 Prise alimentation pour ci

1 Prise RCA pour ci

1 Connecteur DB9 mêle pour ci

1 Circuit imprimé réf. = S362

Assemblage des deux modules

Une fois que le module de contrôle a été assemblé (figures 14 et 15), il faut interconnecter les deux platines, l’une au-dessus de l’autre, comme pour former un sandwich (voir photo en début d’article).

Utiliser pour cela des embases à picots droits, simple rangée, sécables, ou des connecteurs car te à car te, à picots longs d’au moins 20 mm, en regard desquels vous devrez fixer des embases femelles de même diamètre.

Il y a deux liaisons à créer en correspondance de l’arrivée du signal vidéo ;

11 autres liaisons pour les lignes de bus (dont 8 pour les données, une pour le signal d’horloge, une pour le Reset et une pour le FREEZE) et, enfin, deux autres liaisons, situées au prolongement des lignes de bus, portant l’une le +5 volts et l’autre la masse. Il faudra ensuite enficher les deux cartes.

Le montage étant terminé, il ne reste plus qu’à relier le digitaliseur au port série du PC, moyennant un câble pour modem, et installer le logiciel de gestion (voir figure 18) dans le disque dur.

Figure 17: Les deux platines se montent l’une au-dessus de l’autre, comme pour former un sandwich. Utilisez d’un côté des picots droits, longs au moins 20 mm, et de l’autre des embases femelles adaptées, ou des supports tulipe.

Figure 17: Les deux platines se montent l’une au-dessus de l’autre, comme pour former un sandwich. Utilisez d’un côté des picots droits, longs au moins 20 mm, et de l’autre des embases femelles adaptées, ou des supports tulipe.Le logiciel qui gère ce digitaliseur s’appelle GRABSER

Figure 18 : Le logiciel de gestion.

Figure 18 : Le logiciel de gestion.L’interface graphique qui s’ouvre après l’avoir lancée, est constituée de deux parties : d’un côté (la plus grande partie de l’écran) l’image fournie par le digitaliseur, et - de l’autre - des boutons et des cases à cocher.

Dans cette partie, du haut en bas, on trouve la zone correspondant au choix de la résolution (faible ou haute), puis celle correspondant au choix des niveaux de gris (16 ou 256), ensuite, celles concernant le mode de capture et de mise en mémoire, avec possibilité d’incruster le jour et l’heure.

Puis, enfin, le bouton qui permet de sortir du programme. Voyons ces commandes, l’une après l’autre.

Lo re fournit une résolution de 200 x 150 points. Hi re fournit une résolution de 400 x 300 points.

Dans la zone correspondant au choix des tons de gris : “16” fournit des images à 16 niveaux de gris, tandis que “256” fournit des images à 256 niveaux de gris. Même si nous ne vous avions rien dit à leur sujet, vous l’auriez deviné, tant l’interface est claire pour ce qui concerne ces deux premières zones.

Venons-en au bouton “Capture”.

Lorsqu’on clique sur ce bouton, le PC demande au module de lui envoyer la dernière image saisie.

Le module principal active alors la ligne FREEZE, et le microcontrôleur (SCENIX) du digitaliseur complète la numérisation de la dernière image qu’il a en cours de traitement et l’envoie au PIC à la vitesse déterminée par les résolutions demandées par l’utilisateur.

Le microcontrôleur élabore les données en tenant compte de tout ce qui lui a été demandé (niveaux de gris) et les transmet en série au PC. Dans cette phase, le nombre des niveaux de gris est déterminant quant à la vitesse de communication et, par conséquent, à l’intervalle séparant deux images successives.

Si l’on a demandé une image à 16 niveaux de gris, le PIC envoie deux pixels par image.

En cliquant sur “Continu” à côté de la touche “Capture”, on demande une numérisation cyclique ; le système mémorise alors les images en continu et met cycliquement à jour l’écran vir tuel. Lorsque ce mode de fonctionnement a été choisi, un voyant carré passe au rouge pendant tout le temps nécessaire à la digitalisation de l’image en cours, et passe au ver t à la fin de chaque prise de vue.

La touche “Enregistrer image” permet d’enregistrer l’image présente à l’écran sur le disque dur.

La mémorisation se fait dans le dossier sous le nom duquel le logiciel a été installé, en format bitmap ; donc : avec l’extension .bmp.

En cliquant sur “Continu” à côté de la touche “Enregistrer image” on mémorise sur le disque dur toutes les images en suivant, toujours au format bitmap.

Pour les différencier l’une de l’autre, le logiciel leur attribue à chacune la date et l’heure du moment de la capture.

Enfin, la touche “Date/Heure” provoque l’incrustation de la date et de l’heure dans l’image (paramètres se référant, évidemment, à l’horloge de la carte mère) comme on peut le voir, en haut à gauche, sur l’illustration.

Aucun commentaire:

Enregistrer un commentaire