Facilement réalisable, cette carte se connecte au port parallèle du PC. Elle est contrôlée par un programme écrit en QBasic que chacun peut modifier et adapter à d’autres applications.

Elle permet de mesurer et d’exploiter les possibilités offertes par le digitaliseur vidéo que nous avons présenté le mois dernier.

Voici un circuit qui, associé à un module digitaliseur, permet d’effectuer des captures personnalisables.

Généralités

Le module digitaliseur - c’est-à-dire la partie du système qui capture l’image et la digitalise, et auquel cette carte de test est associée - reste exactement le même que celui décrit le mois dernier et assure les mêmes prestations.

La carte que nous décrivons se connecte au port parallèle du PC. Mais, comme vous devez vous en douter, la différence entre le précédent projet et celui-ci, ne réside pas seulement dans le fait qu’au lieu de se connecter au port série il se connecte au port parallèle du PC. Ses caractéristiques sont résumées en figure 1.

La principale différence vient du fait que la gestion du module se fait au moyen d’un programme écrit en QBasic, langage fourni de base avec tout nouveau PC, au même titre que le DOS.

Une autre différence est que cette carte est beaucoup plus simple et ne comprend que des portes logiques.

Bref : pour ceux qui veulent se familiariser avec les nouvelles techniques liées à la capture et au traitement d’images, elle représente la meilleure occasion pour effectuer les premiers pas et découvrir les possibilités de ce nouveau genre d’appareil.

L’une de ces possibilités, par exemple, est la capture d’images sous DOS. Aussi, pour ceux d’entre vous qui ont des connaissances en programmation, elle permet de toucher de plus près les mécanismes fondamentaux qui régissent le module digitaliseur et qui, une fois assimilés, pourraient donner des idées pour toutes sortes d’applications, des plus simples aux plus complexes.

C’est pourquoi, si vous avez trouvé intéressant le projet présenté le mois dernier, mais, plutôt que d’un système clés en main, vous avez besoin d’un appareil permettant de digitaliser un signal vidéo à gérer à votre guise en utilisant le langage de programmation qui vous est le plus familier (Basic, C, Delphi, etc.), alors n’hésitez pas à vous investir dans la réalisation de cette carte d’interface.

Vous n’aurez qu’à l’associer au module digitaliseur (auquel il se superpose comme pour former un sandwich) et à connecter le tout à la LPT de votre PC. Dès lors, vous pourrez vous livrer à toutes sortes d’expériences.

Il n’y a dans cette réalisation aucune complexité, du fait que l’on fait appel au même module digitaliseur de la fois passée, auquel on associe, cette fois, un circuit de contrôle qui est en fait une interface port parallèle, comprenant très peu d’électronique.

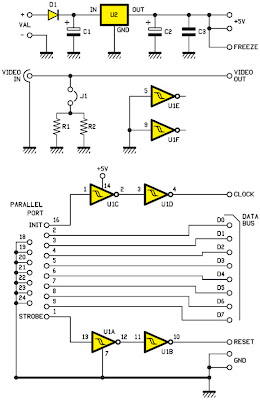

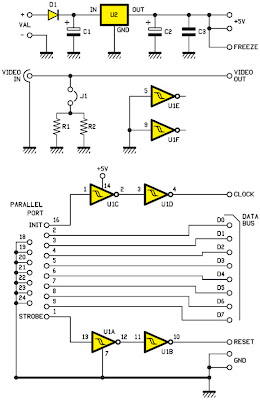

Il suffit de regarder le schéma électrique de cette carte (figure 2), pour vous rendre compte qu’elle ne comporte qu’une petite poignée de composants, qui ne sont pour l’essentiel que des portes logiques. En effet, le principal de cette réalisation n’est pas, à vrai dire, dans le “hard”, mais dans le “soft” que chacun peut modifier ou écrire.

Après ces généralités, passons aux détails.

Figure 1 : Caractéristiques de la carte de test.

Analyse du circuit

Le module de contrôle reçoit le signal vidéo composite sur un connecteur RCA, et l’achemine aux deux points de contact qui l’amènent au digitaliseur (grabber).

Sur le chemin, un cavalier (J1) permet de connecter ou déconnecter deux résistances de 150 ohms branchées en parallèle, formant ainsi une résistance totale de 75 ohms pouvant constituer une charge dont l’utilité dépend des caractéristiques du système vidéo avec lequel on veut travailler.

A ce sujet, il convient de préciser que le module d’acquisition du signal vidéo (le grabber) ne comporte aucune résistance de charge. Son impédance d’entrée est donc beaucoup plus élevée que 75 ohms. Par conséquent, s’il devait être relié en aval d’une caméra ou d’une source vidéo, il pourrait être nécessaire d’insérer une charge en parallèle sur la ligne de liaison, adaptée, tour à tour, aux caractéristiques de la source.

La raison en est que, comme nous l’avions laissé entendre dans la présentation initiale de cette série d’articles, nous comptons associer notre digitaliseur à plusieurs sortes de modules, différents selon les usages.

C’est pour cela que nous n’avons prévu aucune résistance de charge dans le module digitaliseur. Il nous a paru plus logique de l’implanter sur le module qui lui serait associé, de sorte à l’adapter au cas par cas.

En plus, le cavalier amovible permet, soit de la prendre en compte, soit de l’ignorer. Car, à supposer qu’au lieu de se connecter à une source vidéo, le système devait se connecter en parallèle à un câble coaxial reliant une caméra à un moniteur ou à un magnétoscope, il serait inutile de brancher cette résistance, car en pareil cas, elle aurait pour effet d’atténuer le signal, et probablement même d’introduire une détérioration des images en cours de saisie ou enregistrées, du fait que la source vidéo est déjà convenablement chargée, soit par le moniteur, soit par le magnétoscope.

Pour l’alimentation du circuit, on fait appel à un régulateur intégré 7805 qui stabilise à 5 volts la tension continue appliquée sur le bornier d’entrée (VAL).

D1 est une diode de protection. Elle sert à éviter qu’une éventuelle inversion de polarités en entrée endommage irrémédiablement les circuits alimentés derrière.

Remarquez que cette tension de 5 volts sert à la fois à alimenter l’interface et le module digitaliseur, car elle aboutit aussi au peigne de contacts qui assurent les échanges entre les deux cartes.

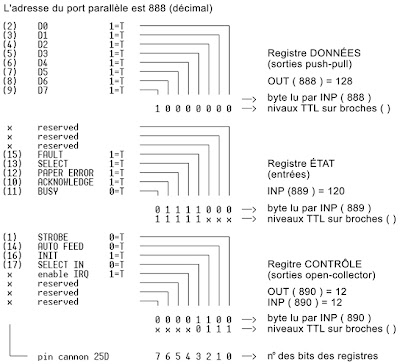

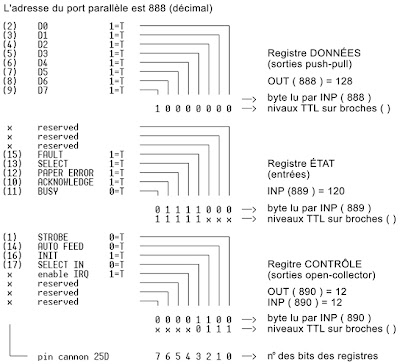

La liaison au PC se fait moyennant un connecteur SubD 25 points coudé pour circuits imprimés, lequel prélève les 8 bits de la LPT, plus les quelques signaux normalement prévus par le standard EPP (Enhanced Parallel Port) pour la gestion de l’imprimante (voir la figure 3).

Le bus des données (D0 à D7) est évidemment réservé au transfert des informations de la RAM au PC.

Les deux autres lignes sont utilisées l’une pour le Clock du module d’acquisition vidéo, et l’autre pour le Reset.

Il s’agit plus exactement du signal STROBE (ligne 1) agissant sur le RESET du module, et du signal INIT (ligne 16) fournissant le signal d’horloge.

Toutes les lignes du bus sont connectées directement, sauf celles relatives au STROBE et à INIT qui sont l’une et l’autre bufférisées par deux inverseurs à trigger de Schmitt placés en série.

Le but de cette architecture est de renforcer et de rendre parfaitement carrés les créneaux générés par le PC. Car le module digitaliseur exige des signaux extrêmement nets et précis, faute de quoi il y aurait perte de synchronisation entre images lues et images échantillonnées, et consécutive perte de lignes dans le photogramme (frame) en construction.

Vous remarquerez au passage que l’entrée FREEZE du digitaliseur n’est pas gérée, mais directement reliée à la ligne positive de l’alimentation. De ce fait, elle est constamment maintenue à l’état haut.

Il en résulte un échantillonnage continu des images et un rafraîchissement permanent des données placées en sortie sur le port parallèle du PC.

Cela équivaut à travailler aux limites des possibilités des circuits. Car l’échantillonnage d’images en mouvement pourrait produire en sortie des photogrammes légèrement hachurés, à cause du fait que la mémoire du module est continuellement mise à jour.

Cependant, étant donné que le transfert des données sur le port de l’imprimante se fait en un temps très court, il y a pratiquement peu de risques d’y voir apparaître des stries, sauf à filmer des objets en mouvement extrêmement rapide. Nous y reviendrons.

Aucun tampon n’étant prévu pour le stockage des données et tout se faisant à la continue, le PC prélève et visualise les informations quasiment en temps réel.

Au fur et à mesure que le digitaliseur échantillonne une image, celle-ci est aussitôt écrite dans la mémoire de l’interface.

Le tout, sous le contrôle d’un programme bien structuré, que nous verrons plus loin.

Mais, avant d’en arriver là, revenons sur la théorie qui est à la base du fonctionnement du module d’acquisition (le grabber), de manière à comprendre comment le PC fabrique les images et les visualise à l’écran.

Figure 2: Schéma électrique de la carte de test.

Figure 2: Schéma électrique de la carte de test.

Le port parallèle

Figure 3 : Le port parallèle.

Figure 3 : Le port parallèle.

La liaison entre le digitaliseur et le PC se fait par le port parallèle. Il s’agit de la LPT1, que l’on appelle plus couramment port imprimante, dont l’adresse hexa est 378. C’est l’adresse que nous reprenons dans notre programme de gestion.

Le port parallèle est une interface qui a toujours existé sur les PC, depuis ceux de la première génération (XT) aux plus modernes (Pentium III et Athlon).

A l’origine (d’où son nom), il avait été prévu exclusivement pour pouvoir y connecter une imprimante. C’est pourquoi certaines de ses broches portent des noms qui se réfèrent précisément aux fonctions propres aux imprimantes.

Rapportée à notre hard, cette prise aboutit à 3 registres : Data Register (le registre des données), Status Register (le registre d’état) et Control Register (le registre de contrôle), chacun avec une fonction précise.

Le premier contient le bus des données qui (sauf dans les tout premiers PC) est bidirectionnel : les données peuvent aller du PC vers l’extérieur (sortir) ou de l’extérieur vers le PC (entrer).

Le bit le moins significatif (D0) aboutit à la patte 2 du connecteur, tandis que le bit le plus fort poids (D7) aboutit à la patte 9.

Dans le registre d’état sont groupés les principaux messages que l’imprimante envoie au PC. Il s’agit donc d’un registre d’entrée.

Les états sont 5 : Fault (patte 15), Select (patte 13), Paper error (patte 12), Acknowledge (patte 10) et Busy (patte 11).

Le premier signale une erreur de liaison ou une panne de communication.

Le troisième signale une panne dans l’alimentation papier (plus de feuilles dans le chargeur de l’imprimante).

Le quatrième répond pour dire qu’il a reconnu les données reçues par le Data Register, et Busy est actif lorsque l’imprimante est mise off line (en mode local).

Le registre de contrôle contient 5 autres signaux avec lesquels le PC contrôle l’activité de l’imprimante.

Parmi ceux-ci, nous en utilisons deux : un pour fournir le signal d’horloge, et l’autre pour fournir le Reset au module digitaliseur.

À la lumière de ce qui vient d’être dit, on devrait être à même de comprendre la signification de quelques-unes des lignes du programme de gestion du module.

PORTBASE définit le port à utiliser (ici : LPT, c’est-à-dire &H378). La ligne STATUS=… spécifie la configuration du registre d’état. CONTROL=… spécifie la configuration du registre de contrôle. Tandis que EPPDATA définit le registre des données.

Enfin CLOCK=4 dit quel est le bit du registre de contrôle duquel sort le signal d’horloge destiné au digitaliseur, et RESET=1 précise la même chose à l’égard du signal de Reset.

Le module digitaliseur

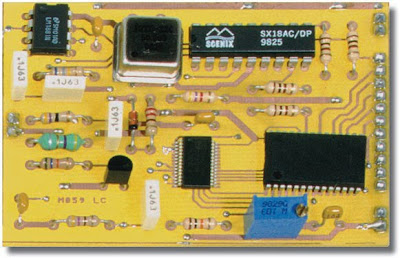

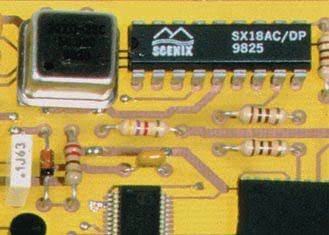

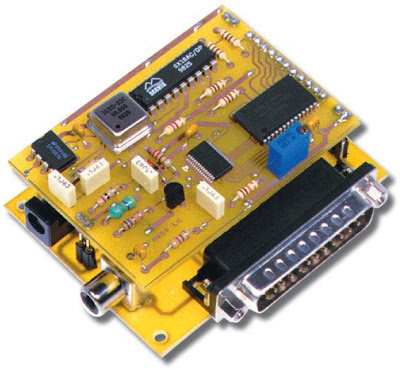

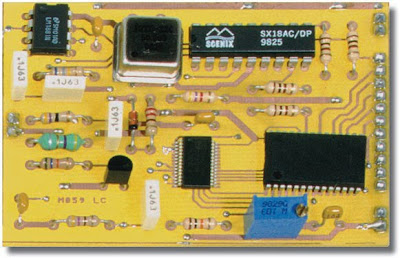

Figure 4a : Photo de l’une de nos réalisations du module digitaliseur (grabber) auquel la carte de test est reliée.

Figure 4a : Photo de l’une de nos réalisations du module digitaliseur (grabber) auquel la carte de test est reliée.

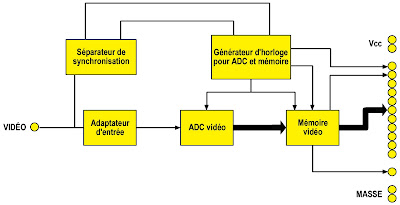

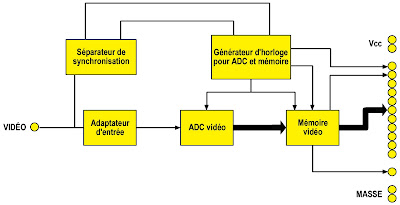

Figure 4b : Schéma synoptique du module vidéo.

Figure 4b : Schéma synoptique du module vidéo.

Notre système est en fait constitué de deux cartes.

Celle qui effectue la digitalisation à proprement parler (le grabber) est un module autonome, à broches enfichables.

L’échantillonnage est effectué par un convertisseur A/D à 8 bits. Le stockage des données se fait dans une RAM de 3 mégabits sous le contrôle d’un microcontrôleur SCENIX SX18 travaillant à une fréquence horloge de 50 MHz.

Rappel du fonctionnement du module digitaliseur

Nous parlons ici du module qui prélève le signal vidéo et l’échantillonne (voir la figure 4a).

L’échantillonnage est effectué par un convertisseur analogique/digital à 8 bits, conformément au synoptique de la figure 4b.

Les grandeurs issues de la conversion sont transférées dans une RAM à deux pages, un photogramme à la fois.

Les images d’une prise de vue vidéo se suivent l’une après l’autre.

Le bus auquel la RAM est reliée en permet le contrôle de l’extérieur.

On peut donc aller chercher les données et les mettre sur le port parallèle en format 8 bits.

Autrement dit : une fois que la grandeur du signal vidéo a été échantillonnée, les données relatives à chaque pixel sont stockées dans la RAM externe, dont la taille est assez grande pour contenir toutes les informations se rapportant à un photogramme.

A partir de là, le module d’interface peut mettre les données en sortie.

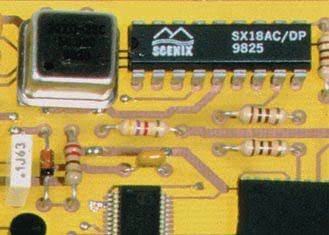

Le signal d’horloge qui cadence la conversion est généré par un microcontrôleur (voir détail en figure 5), lequel préside à toutes les fonctions du module.

Il s’agit d’un SCENIX SX18 travaillant avec un résonateur à 50 MHz. Ce microcontrôleur se synchronise avec les tops de ligne et de trame contenus dans le signal vidéo et fournis séparément par un circuit EL4581 séparateur de tops synchro.

Les informations respectives lui servent pour reconstituer la trame d’une image. Plus exactement, le top de synchronisation de trame est utilisé pour le rafraîchissement de la mémoire et pour signaler au microcontrôleur à quel moment précis se termine l’acquisition d’un photogramme, tandis que le top de synchro ligne sert à cadencer le convertisseur A/D et la mémoire, car il renseigne du moment auquel chaque ligne commence et finit.

Autrement dit : le microcontrôleur récupère - à partir du balayage horizontal - le pixel-clock (PIXCLK) qu’il envoie à la fois sur le convertisseur A/D et sur la partie de la RAM réservée à l’écriture (WCK), et, à partir du balayage vertical, l’information lui indiquant précisément à quel moment se termine l’écriture d’un photogramme dans la RAM.

Etant donné qu’il faut composer avec l’espace mémoire total disponible, chaque cadrage est digitalisé au format max de 400 x 300 pixels. Ce qui conduit à une définition totale de 120 000 pixels.

Chaque pixel, bien que mémorisé à une vitesse bien inférieure à la vitesse standard, qui est de 15,625 kHz, est néanmoins synchronisé à la vitesse des impulsions horizontales contenues dans la vidéo composite.

Puisque le signal d’horloge qui pilote le convertisseur A/D agit aussi sur l’entrée WCK, les informations échantillonnées sont transférées dans la portion de RAM destinée à l’écriture, au même rythme et en parfaite correspondance.

Il en résulte le fonctionnement suivant : au démarrage d’une trame, le séparateur de tops (un EL4581) fournit au microcontrôleur une impulsion de synchro verticale que celui-ci utilise pour mettre à zéro la mémoire (via WRTS) et pour commencer à compter les emplacements, à partir de l’adresse zéro.

Pendant ce temps-là, le convertisseur A/D (Philips TDA8761) est inopérant, jusqu’à ce que le microcontrôleur SCENIX lui envoie une impulsion d’horloge.

A l’arrivée de la première impulsion, deux choses démarrent alors simultanément : le convertisseur A/D lit le signal qui arrive sur son entrée, et échantillonne le niveau analogique du premier pixel en le transformant en format digital sur 8 bits.

Il s’ensuit un octet aussitôt écrit dans la portion de RAM destinée à l’écriture, étant donné que le même signal d’horloge, qui incrémente le convertisseur A/D, incrémente aussi, en même temps, les adresses de la RAM.

Par conséquent, l’octet contenant l’information relative au premier pixel est écrit dans le premier emplacement mémoire.

Puis arrive la deuxième impulsion.

Alors, le convertisseur échantillonne et met sur le data-bus de la RAM l’octet relatif au deuxième pixel. Puis, à la troisième impulsion, il fait de même avec le troisième octet… et ainsi de suite, jusqu’au 400e.

Inutile de préciser que la fin d’une ligne n’a pas le même effet que la fin d’une image.

Le signal relatif à la fin d’une ligne a une valeur purement informative pour le SX18. Celui-ci l’utilise exclusivement pour savoir à quel instant il doit faire partir le balayage suivant.

Il n’en va pas de même du signal relatif à la fin d’une image. Car, une fois que les 300 lignes constituant la totalité d’une image ont été analysées, 120 000 octets ont été écrits dans la RAM. Celle-ci est pleine.

C’est alors qu’à l’arrivée du top de la synchro verticale suivant, le microcontrôleur SCENIX en génère un, lui, avec lequel il déclenche un Reset de la RAM.

De cette manière, la RAM s’étant vidée, les nouvelles données que le convertisseur A/D lui envoie à partir de maintenant, commencent à s’écrire à partir de l’adresse zéro.

Recommence ainsi un nouveau cycle. Les nouvelles données sont écrites à la place des précédentes, et chaque nouvelle ligne remplace l’ancienne.

Cette façon de travailler détermine le résultat visuel que l’on peut obtenir, et qui dépend pour beaucoup de comment l’utilisateur va lire la mémoire.

Si, par exemple, on filmait une image passant devant la caméra à très grande vitesse, il est évident que celle-ci serait affectée d’un certain flou.

Ce serait comme si, par analogie à un appareil photo, on photographiait une voiture de course défilant à 300 km/heure, avec un temps d’obturation long.

Or c’est là justement qu’intervient la ligne FREEZE. Lorsque celle-ci est mise à l’état bas, elle “gèle” (to freeze), c’est-à-dire elle bloque le fonctionnement du microcontrôleur et, par conséquent, le balayage de l’image.

Dès lors, le pixel-clock est arrêté, et l’écriture en RAM de toute nouvelle donnée est aussi arrêtée.

Figure 5 : Gros plan sur le microcontrôleur SCENIX entouré du résonateur à 50 MHz, de la RAM vidéo et (partiellement visible) du convertisseur A/D.

Figure 5 : Gros plan sur le microcontrôleur SCENIX entouré du résonateur à 50 MHz, de la RAM vidéo et (partiellement visible) du convertisseur A/D.

Le fonctionnement dans son ensemble

En sachant comment sont faits chacun des deux modules, on peut voir maintenant ce qu’ils font quand ils sont reliés ensemble, en ayant à l’esprit qu’à partir de là, c’est le PC qui prend la main et qui en coordonne l’activité.

Le digitaliseur fonctionne continuellement et de façon autonome.

Il échantillonne le signal vidéo composite et écrit en RAM les données issues de la conversion.

Pour lire les données écrites dans la mémoire, le PC envoie premièrement une impulsion de Reset (par la ligne STROBE).

Puis il envoie des impulsions d’horloge au rythme desquelles il démarre la scrutation séquentielle de chaque octet correspondant aux pixels respectifs de l’image à recomposer.

Chaque octet, élaboré par la routine du soft, est ensuite visualisé, produisant, à un endroit défini de l’écran, un certain niveau de gris. Autrement dit, une certaine brillance de l’écran.

L’ensemble des pixels construit l’image filmée.

La mise à jour des images se fait toutes les deux secondes, ce qui produit un photogramme (frame) toutes les deux secondes. C’est le temps requis pour visualiser chaque vue.

La résolution d’une image noir et blanc est maximale. Celle-ci est de 400 x 300 points, bien que l’écran la restitue au format 640 x 480.

La définition est sur 16 niveaux de gris.

La raison de toutes ces précisions deviendra plus évidente dans un instant, lors de l’examen du contenu du programme écrit pour la gestion du système (voir figure 6).

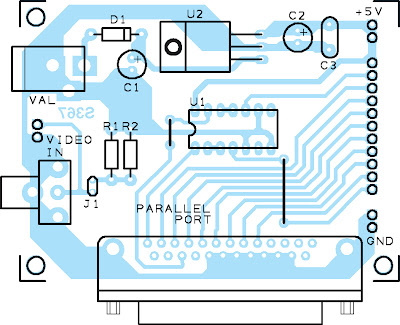

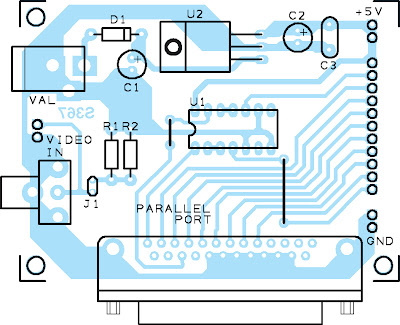

Figure 7 : Schéma d’implantation des composants de la carte de test.

Figure 7 : Schéma d’implantation des composants de la carte de test.

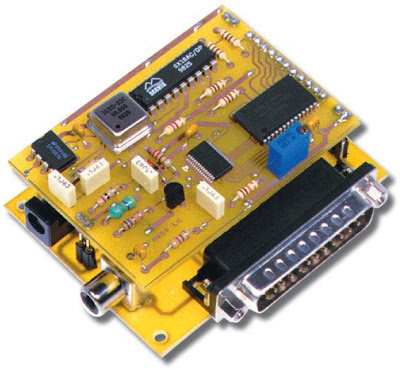

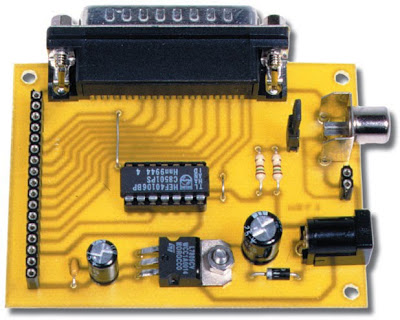

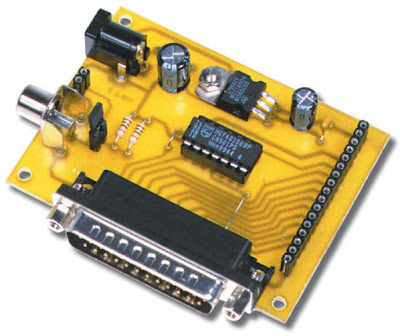

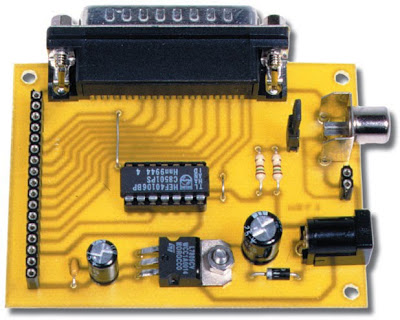

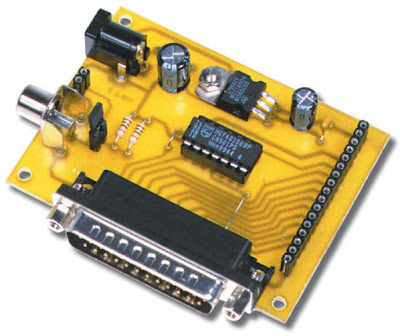

Figure 8 : La carte de test à montage terminée.

Figure 8 : La carte de test à montage terminée.

Le connecteur RCA peut recevoir un signal vidéo composite en provenance de n’importe quelle source vidéo.

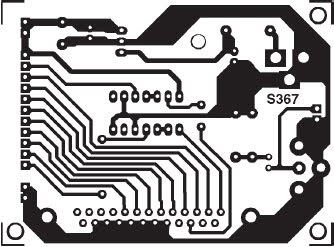

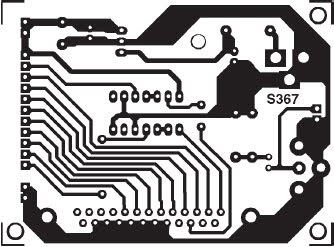

Figure 9 : Dessin, à l’échelle 1, du circuit imprimé de la carte de test servant d’interface entre le digitaliseur et le PC.

Figure 9 : Dessin, à l’échelle 1, du circuit imprimé de la carte de test servant d’interface entre le digitaliseur et le PC.

Liste des composants

R1 = 150 Ω

R2 = 150 Ω

C1 = 220 μF 25 V électrolytique

C2 = 10 μF 16 V électrolytique

C3 = 100 nF multicouche

U1 = Intégré CD40106

U2 = Régulateur 7805

D1 = Diode 1N4007

Divers :

1 Support 2 x 7 broches

1 Prise RCA pour ci

1 Prise alimentation pour ci

1 Connecteur DB25 mâle pour ci

1 Connecteur strip femelle

19 pôles

1 Connecteur strip mâle

2 pôles

1 Cavalier

1 Circuit imprimé réf. S367

Figure 10 : La liaison au PC se fait sur le port parallèle par un connecteur mâle SubD 25 points.

Figure 10 : La liaison au PC se fait sur le port parallèle par un connecteur mâle SubD 25 points.

La carte utilise les 8 bits de données de la LPT plus quelques-uns des signaux faisant partie du standard EPP (Enhanced Parallel Port).

Le programme

Les premières instructions concernent la définition des variables utilisées.

Plus précisément, 400 représente le nombre de colonnes constituant une image (VIDPIX), 300 représente le nombre de lignes (VIDLINES), &H378 représente l’adresse de base du port parallèle (PORTBSE = &H378). Puis viennent les trois registres associés à ce port : le Control Register, le Data Register et le Status Register.

Enfin, nous associons le mnémonique RESET à la ligne 1 du port parallèle, et le mnémonique CLOCK à la ligne 4.

L’instruction SCREEN définit le mode de fonctionnement de l’écran. Elle définit la résolution. Ici, elle est de 640 x 480 x 16 couleurs.

Les couleurs sont redéfinies par l’instruction PALETTE du Basic.

Vous remarquerez au passage que de cette façon, le maximum des couleurs possibles est 16, et que 16 est aussi le nombre maximum des niveaux de gris.

Après les indispensables déclarations et les configurations, on passe au programme proprement dit. Celui-ci est en fait constitué d’une boucle entre DO et LOOP.

A l’intérieur de cette boucle, il y a l’instruction INKEY$ qui fait arrêter l’exécution du programme lorsqu’on appuie sur une quelconque touche du clavier.

Le cycle démarre par l’envoi d’un état logique haut sur la ligne de Reset (STROBE) et sur celle de Clock (INIT).

Le pas suivant prévoit le maintient à l’état haut du Reset, et la mise à zéro du Clock.

Puis l’un et l’autre sont mis à zéro.

Ces commandes constituent en fait un cycle qui permet d’effectuer la mise à zéro des lignes d’adresses de la RAM à deux pages, pour que le digitaliseur y accède à partir de l’adresse zéro.

En effet, pour effacer la mémoire, une simple impulsion positive sur la patte Reset ne suffit pas. Il faut y associer une transition 0/1 sur la patte du Clock, alors que Reset est encore à 1.

Après l’initialisation de la mémoire (mise à zéro du compteur d’adresses), commence l’extraction des données : à chaque cycle d’horloge (0/1 logique) obtenu par les instructions OUT CONTROL, 32 OR CLOCK (Clock = 1) et OUT CONTROL, 32 (Clock = 0), on lit l’octet disponible sur le bus des données D0 à D7 du port parallèle.

L’octet lu sur ces lignes est stocké dans la variable “data” par l’instruction data = INP (EPPDATA).

Puis vient l’instruction PSET qui traite le pixel selon l’état de ses 8 bits, en choisissant les couleurs sur la base d’une palette noir et blanc, c’est-à-dire limitée à 16 combinaisons. C’est la raison pour laquelle l’octet est divisé par 16.

En effet (256 : 16) = 16.

Dès lors, l’instruction NEXT pixel lance un nouveau cycle : nouveau coup d’horloge, acquisition d’un nouvel octet, division et affichage d’un autre point.

Le tout pendant le nombre de fois défini par VIDPIX (ici 400) correspondant au nombre de pixels formant une ligne image.

Après l’affichage de la première ligne, on passe à la deuxième, et ainsi de suite. Jusqu’à ce que le programme atteigne VIDLINES : la dernière ligne.

Les instructions LOCATE 18,2 et PRINT DATE$… servent à faire apparaître à l’écran la date et l’heure courante, sur la base de l’horloge interne du PC.

Plus précisément : LOCATE précise à quel endroit la ligne doit s’écrire, alors que PRINT provoque l’affichage de la date et l’heure, en noir et blanc.

Réalisation pratique

Une fois imprégnés de la façon dont vont les choses, tant pour ce qui concerne la partie électronique que pour ce qui concerne le programme, on peut passer à la réalisation pratique.

Le circuit imprimé de cette carte est un simple face à réaliser par photogravure, en partant d’une photocopie sur mylar du tracé donné tel quel en figure 9.

Vous monterez les composants en partant des plus bas pour terminer par les plus hauts, en vous référant au schéma d’implantation des composants de la figure 7 et à la photo du montage terminé de la figure 8.

En réalité, il y a peu de composants à souder.

Aussi vous commencerez par les résistances et la diode D1 dont il faut respecter les polarités.

Continuez avec le support du circuit imprimé U1 (CD40106) dont le détrompeur doit être tourné du côté du petit strap. Puis soudez les condensateurs.

Pliez les pattes du régulateur U2 afin de le monter à plat (attention au trou de fixation).

Fixez à l’aide d’une vis, rondelle et écrou. Soudez.

Puis installez le connecteur mâle SubD 25 points coudé pour circuit imprimé.

Poussez-le à fond avant de commencer à le souder, afin de lui assurer la meilleure tenue mécanique.

Pour ce qui concerne l’alimentation, comme vous utiliserez vraisemblablement un bloc secteur, vous installerez une embase à souder de type adapté.

L’entrée vidéo se fait sur une embase RCA pour circuit imprimé.

N’oubliez pas les deux straps. Ni le cavalier J1, placé derrière l’embase RCA. Vous veillerez à le laisser normalement fermé.

Les figures 9, 10 et 11 montrent le résultat auquel vous devriez arriver.

Reliez ensuite cette carte à celle du module digitaliseur, avec laquelle elle forme une sorte de sandwich. Puis effectuez tous les branchements.

La liaison au PC se fait au moyen d’un câble imprimante à 25 conducteurs.

Pour ce qui concerne le programme, avant d’en essayer un de votre cru, recopiez le nôtre en utilisant l’éditeur du DOS, dans un fichier auquel vous donnerez un nom (celui que vous voulez), terminé impérativement par l’extension .BAS.

Puis, toujours sous DOS, appelez QBasic suivi du nom du fichier que vous avez donné au programme.

Une fois le fichier ouvert avec QBasic, lancez-le par la commande RUN.

Dès lors vous verrez les images venir à l’écran, en haut à gauche, avec, dans le bas, la date et l’heure. Les images sont mises à jour toutes les deux secondes.

Pour arrêter la visualisation des images, il suffit d’appuyer sur une quelconque touche du clavier, ce qui provoque la sortie du programme, et le retour à QBasic et à l’environnement DOS.

Figure 11 : La carte de test et le module digitaliseur se placent l’un sur l’autre et s’interconnectent au moyen de broches mâles et de contacts femelles.

Figure 11 : La carte de test et le module digitaliseur se placent l’un sur l’autre et s’interconnectent au moyen de broches mâles et de contacts femelles.

Elle permet de mesurer et d’exploiter les possibilités offertes par le digitaliseur vidéo que nous avons présenté le mois dernier.

Voici un circuit qui, associé à un module digitaliseur, permet d’effectuer des captures personnalisables.

Généralités

Le module digitaliseur - c’est-à-dire la partie du système qui capture l’image et la digitalise, et auquel cette carte de test est associée - reste exactement le même que celui décrit le mois dernier et assure les mêmes prestations.

La carte que nous décrivons se connecte au port parallèle du PC. Mais, comme vous devez vous en douter, la différence entre le précédent projet et celui-ci, ne réside pas seulement dans le fait qu’au lieu de se connecter au port série il se connecte au port parallèle du PC. Ses caractéristiques sont résumées en figure 1.

La principale différence vient du fait que la gestion du module se fait au moyen d’un programme écrit en QBasic, langage fourni de base avec tout nouveau PC, au même titre que le DOS.

Une autre différence est que cette carte est beaucoup plus simple et ne comprend que des portes logiques.

Bref : pour ceux qui veulent se familiariser avec les nouvelles techniques liées à la capture et au traitement d’images, elle représente la meilleure occasion pour effectuer les premiers pas et découvrir les possibilités de ce nouveau genre d’appareil.

L’une de ces possibilités, par exemple, est la capture d’images sous DOS. Aussi, pour ceux d’entre vous qui ont des connaissances en programmation, elle permet de toucher de plus près les mécanismes fondamentaux qui régissent le module digitaliseur et qui, une fois assimilés, pourraient donner des idées pour toutes sortes d’applications, des plus simples aux plus complexes.

C’est pourquoi, si vous avez trouvé intéressant le projet présenté le mois dernier, mais, plutôt que d’un système clés en main, vous avez besoin d’un appareil permettant de digitaliser un signal vidéo à gérer à votre guise en utilisant le langage de programmation qui vous est le plus familier (Basic, C, Delphi, etc.), alors n’hésitez pas à vous investir dans la réalisation de cette carte d’interface.

Vous n’aurez qu’à l’associer au module digitaliseur (auquel il se superpose comme pour former un sandwich) et à connecter le tout à la LPT de votre PC. Dès lors, vous pourrez vous livrer à toutes sortes d’expériences.

Il n’y a dans cette réalisation aucune complexité, du fait que l’on fait appel au même module digitaliseur de la fois passée, auquel on associe, cette fois, un circuit de contrôle qui est en fait une interface port parallèle, comprenant très peu d’électronique.

Il suffit de regarder le schéma électrique de cette carte (figure 2), pour vous rendre compte qu’elle ne comporte qu’une petite poignée de composants, qui ne sont pour l’essentiel que des portes logiques. En effet, le principal de cette réalisation n’est pas, à vrai dire, dans le “hard”, mais dans le “soft” que chacun peut modifier ou écrire.

Après ces généralités, passons aux détails.

| Entrée série pour signal vidéo composite |

| Se branche sur le port parallèle (imprimante) de n’importe quel PC |

| Gestion logicielle assurée par un programme écrit en QBasic |

| Définition des images sous 16 niveaux de gris |

| Résolution image de 400 x 300 points |

| Intervalle entre deux captures successives : 2 secondes |

Analyse du circuit

Le module de contrôle reçoit le signal vidéo composite sur un connecteur RCA, et l’achemine aux deux points de contact qui l’amènent au digitaliseur (grabber).

Sur le chemin, un cavalier (J1) permet de connecter ou déconnecter deux résistances de 150 ohms branchées en parallèle, formant ainsi une résistance totale de 75 ohms pouvant constituer une charge dont l’utilité dépend des caractéristiques du système vidéo avec lequel on veut travailler.

A ce sujet, il convient de préciser que le module d’acquisition du signal vidéo (le grabber) ne comporte aucune résistance de charge. Son impédance d’entrée est donc beaucoup plus élevée que 75 ohms. Par conséquent, s’il devait être relié en aval d’une caméra ou d’une source vidéo, il pourrait être nécessaire d’insérer une charge en parallèle sur la ligne de liaison, adaptée, tour à tour, aux caractéristiques de la source.

La raison en est que, comme nous l’avions laissé entendre dans la présentation initiale de cette série d’articles, nous comptons associer notre digitaliseur à plusieurs sortes de modules, différents selon les usages.

C’est pour cela que nous n’avons prévu aucune résistance de charge dans le module digitaliseur. Il nous a paru plus logique de l’implanter sur le module qui lui serait associé, de sorte à l’adapter au cas par cas.

En plus, le cavalier amovible permet, soit de la prendre en compte, soit de l’ignorer. Car, à supposer qu’au lieu de se connecter à une source vidéo, le système devait se connecter en parallèle à un câble coaxial reliant une caméra à un moniteur ou à un magnétoscope, il serait inutile de brancher cette résistance, car en pareil cas, elle aurait pour effet d’atténuer le signal, et probablement même d’introduire une détérioration des images en cours de saisie ou enregistrées, du fait que la source vidéo est déjà convenablement chargée, soit par le moniteur, soit par le magnétoscope.

Pour l’alimentation du circuit, on fait appel à un régulateur intégré 7805 qui stabilise à 5 volts la tension continue appliquée sur le bornier d’entrée (VAL).

D1 est une diode de protection. Elle sert à éviter qu’une éventuelle inversion de polarités en entrée endommage irrémédiablement les circuits alimentés derrière.

Remarquez que cette tension de 5 volts sert à la fois à alimenter l’interface et le module digitaliseur, car elle aboutit aussi au peigne de contacts qui assurent les échanges entre les deux cartes.

La liaison au PC se fait moyennant un connecteur SubD 25 points coudé pour circuits imprimés, lequel prélève les 8 bits de la LPT, plus les quelques signaux normalement prévus par le standard EPP (Enhanced Parallel Port) pour la gestion de l’imprimante (voir la figure 3).

Le bus des données (D0 à D7) est évidemment réservé au transfert des informations de la RAM au PC.

Les deux autres lignes sont utilisées l’une pour le Clock du module d’acquisition vidéo, et l’autre pour le Reset.

Il s’agit plus exactement du signal STROBE (ligne 1) agissant sur le RESET du module, et du signal INIT (ligne 16) fournissant le signal d’horloge.

Toutes les lignes du bus sont connectées directement, sauf celles relatives au STROBE et à INIT qui sont l’une et l’autre bufférisées par deux inverseurs à trigger de Schmitt placés en série.

Le but de cette architecture est de renforcer et de rendre parfaitement carrés les créneaux générés par le PC. Car le module digitaliseur exige des signaux extrêmement nets et précis, faute de quoi il y aurait perte de synchronisation entre images lues et images échantillonnées, et consécutive perte de lignes dans le photogramme (frame) en construction.

Vous remarquerez au passage que l’entrée FREEZE du digitaliseur n’est pas gérée, mais directement reliée à la ligne positive de l’alimentation. De ce fait, elle est constamment maintenue à l’état haut.

Il en résulte un échantillonnage continu des images et un rafraîchissement permanent des données placées en sortie sur le port parallèle du PC.

Cela équivaut à travailler aux limites des possibilités des circuits. Car l’échantillonnage d’images en mouvement pourrait produire en sortie des photogrammes légèrement hachurés, à cause du fait que la mémoire du module est continuellement mise à jour.

Cependant, étant donné que le transfert des données sur le port de l’imprimante se fait en un temps très court, il y a pratiquement peu de risques d’y voir apparaître des stries, sauf à filmer des objets en mouvement extrêmement rapide. Nous y reviendrons.

Aucun tampon n’étant prévu pour le stockage des données et tout se faisant à la continue, le PC prélève et visualise les informations quasiment en temps réel.

Au fur et à mesure que le digitaliseur échantillonne une image, celle-ci est aussitôt écrite dans la mémoire de l’interface.

Le tout, sous le contrôle d’un programme bien structuré, que nous verrons plus loin.

Mais, avant d’en arriver là, revenons sur la théorie qui est à la base du fonctionnement du module d’acquisition (le grabber), de manière à comprendre comment le PC fabrique les images et les visualise à l’écran.

Figure 2: Schéma électrique de la carte de test.

Figure 2: Schéma électrique de la carte de test.Le port parallèle

Figure 3 : Le port parallèle.

Figure 3 : Le port parallèle.La liaison entre le digitaliseur et le PC se fait par le port parallèle. Il s’agit de la LPT1, que l’on appelle plus couramment port imprimante, dont l’adresse hexa est 378. C’est l’adresse que nous reprenons dans notre programme de gestion.

Le port parallèle est une interface qui a toujours existé sur les PC, depuis ceux de la première génération (XT) aux plus modernes (Pentium III et Athlon).

A l’origine (d’où son nom), il avait été prévu exclusivement pour pouvoir y connecter une imprimante. C’est pourquoi certaines de ses broches portent des noms qui se réfèrent précisément aux fonctions propres aux imprimantes.

Rapportée à notre hard, cette prise aboutit à 3 registres : Data Register (le registre des données), Status Register (le registre d’état) et Control Register (le registre de contrôle), chacun avec une fonction précise.

Le premier contient le bus des données qui (sauf dans les tout premiers PC) est bidirectionnel : les données peuvent aller du PC vers l’extérieur (sortir) ou de l’extérieur vers le PC (entrer).

Le bit le moins significatif (D0) aboutit à la patte 2 du connecteur, tandis que le bit le plus fort poids (D7) aboutit à la patte 9.

Dans le registre d’état sont groupés les principaux messages que l’imprimante envoie au PC. Il s’agit donc d’un registre d’entrée.

Les états sont 5 : Fault (patte 15), Select (patte 13), Paper error (patte 12), Acknowledge (patte 10) et Busy (patte 11).

Le premier signale une erreur de liaison ou une panne de communication.

Le troisième signale une panne dans l’alimentation papier (plus de feuilles dans le chargeur de l’imprimante).

Le quatrième répond pour dire qu’il a reconnu les données reçues par le Data Register, et Busy est actif lorsque l’imprimante est mise off line (en mode local).

Le registre de contrôle contient 5 autres signaux avec lesquels le PC contrôle l’activité de l’imprimante.

Parmi ceux-ci, nous en utilisons deux : un pour fournir le signal d’horloge, et l’autre pour fournir le Reset au module digitaliseur.

À la lumière de ce qui vient d’être dit, on devrait être à même de comprendre la signification de quelques-unes des lignes du programme de gestion du module.

PORTBASE définit le port à utiliser (ici : LPT, c’est-à-dire &H378). La ligne STATUS=… spécifie la configuration du registre d’état. CONTROL=… spécifie la configuration du registre de contrôle. Tandis que EPPDATA définit le registre des données.

Enfin CLOCK=4 dit quel est le bit du registre de contrôle duquel sort le signal d’horloge destiné au digitaliseur, et RESET=1 précise la même chose à l’égard du signal de Reset.

Le module digitaliseur

Figure 4a : Photo de l’une de nos réalisations du module digitaliseur (grabber) auquel la carte de test est reliée.

Figure 4a : Photo de l’une de nos réalisations du module digitaliseur (grabber) auquel la carte de test est reliée. Figure 4b : Schéma synoptique du module vidéo.

Figure 4b : Schéma synoptique du module vidéo.Notre système est en fait constitué de deux cartes.

Celle qui effectue la digitalisation à proprement parler (le grabber) est un module autonome, à broches enfichables.

L’échantillonnage est effectué par un convertisseur A/D à 8 bits. Le stockage des données se fait dans une RAM de 3 mégabits sous le contrôle d’un microcontrôleur SCENIX SX18 travaillant à une fréquence horloge de 50 MHz.

Rappel du fonctionnement du module digitaliseur

Nous parlons ici du module qui prélève le signal vidéo et l’échantillonne (voir la figure 4a).

L’échantillonnage est effectué par un convertisseur analogique/digital à 8 bits, conformément au synoptique de la figure 4b.

Les grandeurs issues de la conversion sont transférées dans une RAM à deux pages, un photogramme à la fois.

Les images d’une prise de vue vidéo se suivent l’une après l’autre.

Le bus auquel la RAM est reliée en permet le contrôle de l’extérieur.

On peut donc aller chercher les données et les mettre sur le port parallèle en format 8 bits.

Autrement dit : une fois que la grandeur du signal vidéo a été échantillonnée, les données relatives à chaque pixel sont stockées dans la RAM externe, dont la taille est assez grande pour contenir toutes les informations se rapportant à un photogramme.

A partir de là, le module d’interface peut mettre les données en sortie.

Le signal d’horloge qui cadence la conversion est généré par un microcontrôleur (voir détail en figure 5), lequel préside à toutes les fonctions du module.

Il s’agit d’un SCENIX SX18 travaillant avec un résonateur à 50 MHz. Ce microcontrôleur se synchronise avec les tops de ligne et de trame contenus dans le signal vidéo et fournis séparément par un circuit EL4581 séparateur de tops synchro.

Les informations respectives lui servent pour reconstituer la trame d’une image. Plus exactement, le top de synchronisation de trame est utilisé pour le rafraîchissement de la mémoire et pour signaler au microcontrôleur à quel moment précis se termine l’acquisition d’un photogramme, tandis que le top de synchro ligne sert à cadencer le convertisseur A/D et la mémoire, car il renseigne du moment auquel chaque ligne commence et finit.

Autrement dit : le microcontrôleur récupère - à partir du balayage horizontal - le pixel-clock (PIXCLK) qu’il envoie à la fois sur le convertisseur A/D et sur la partie de la RAM réservée à l’écriture (WCK), et, à partir du balayage vertical, l’information lui indiquant précisément à quel moment se termine l’écriture d’un photogramme dans la RAM.

Etant donné qu’il faut composer avec l’espace mémoire total disponible, chaque cadrage est digitalisé au format max de 400 x 300 pixels. Ce qui conduit à une définition totale de 120 000 pixels.

Chaque pixel, bien que mémorisé à une vitesse bien inférieure à la vitesse standard, qui est de 15,625 kHz, est néanmoins synchronisé à la vitesse des impulsions horizontales contenues dans la vidéo composite.

Puisque le signal d’horloge qui pilote le convertisseur A/D agit aussi sur l’entrée WCK, les informations échantillonnées sont transférées dans la portion de RAM destinée à l’écriture, au même rythme et en parfaite correspondance.

Il en résulte le fonctionnement suivant : au démarrage d’une trame, le séparateur de tops (un EL4581) fournit au microcontrôleur une impulsion de synchro verticale que celui-ci utilise pour mettre à zéro la mémoire (via WRTS) et pour commencer à compter les emplacements, à partir de l’adresse zéro.

Pendant ce temps-là, le convertisseur A/D (Philips TDA8761) est inopérant, jusqu’à ce que le microcontrôleur SCENIX lui envoie une impulsion d’horloge.

A l’arrivée de la première impulsion, deux choses démarrent alors simultanément : le convertisseur A/D lit le signal qui arrive sur son entrée, et échantillonne le niveau analogique du premier pixel en le transformant en format digital sur 8 bits.

Il s’ensuit un octet aussitôt écrit dans la portion de RAM destinée à l’écriture, étant donné que le même signal d’horloge, qui incrémente le convertisseur A/D, incrémente aussi, en même temps, les adresses de la RAM.

Par conséquent, l’octet contenant l’information relative au premier pixel est écrit dans le premier emplacement mémoire.

Puis arrive la deuxième impulsion.

Alors, le convertisseur échantillonne et met sur le data-bus de la RAM l’octet relatif au deuxième pixel. Puis, à la troisième impulsion, il fait de même avec le troisième octet… et ainsi de suite, jusqu’au 400e.

Inutile de préciser que la fin d’une ligne n’a pas le même effet que la fin d’une image.

Le signal relatif à la fin d’une ligne a une valeur purement informative pour le SX18. Celui-ci l’utilise exclusivement pour savoir à quel instant il doit faire partir le balayage suivant.

Il n’en va pas de même du signal relatif à la fin d’une image. Car, une fois que les 300 lignes constituant la totalité d’une image ont été analysées, 120 000 octets ont été écrits dans la RAM. Celle-ci est pleine.

C’est alors qu’à l’arrivée du top de la synchro verticale suivant, le microcontrôleur SCENIX en génère un, lui, avec lequel il déclenche un Reset de la RAM.

De cette manière, la RAM s’étant vidée, les nouvelles données que le convertisseur A/D lui envoie à partir de maintenant, commencent à s’écrire à partir de l’adresse zéro.

Recommence ainsi un nouveau cycle. Les nouvelles données sont écrites à la place des précédentes, et chaque nouvelle ligne remplace l’ancienne.

Cette façon de travailler détermine le résultat visuel que l’on peut obtenir, et qui dépend pour beaucoup de comment l’utilisateur va lire la mémoire.

Si, par exemple, on filmait une image passant devant la caméra à très grande vitesse, il est évident que celle-ci serait affectée d’un certain flou.

Ce serait comme si, par analogie à un appareil photo, on photographiait une voiture de course défilant à 300 km/heure, avec un temps d’obturation long.

Or c’est là justement qu’intervient la ligne FREEZE. Lorsque celle-ci est mise à l’état bas, elle “gèle” (to freeze), c’est-à-dire elle bloque le fonctionnement du microcontrôleur et, par conséquent, le balayage de l’image.

Dès lors, le pixel-clock est arrêté, et l’écriture en RAM de toute nouvelle donnée est aussi arrêtée.

Figure 5 : Gros plan sur le microcontrôleur SCENIX entouré du résonateur à 50 MHz, de la RAM vidéo et (partiellement visible) du convertisseur A/D.

Figure 5 : Gros plan sur le microcontrôleur SCENIX entouré du résonateur à 50 MHz, de la RAM vidéo et (partiellement visible) du convertisseur A/D.DEFINT A-ZVIDPIX = 400VIDLINES = 300PORTBASE = &H378STATUS = PORTBASE + 1CONTROL = PORTBASE + 2EPPDATA = PORTBASE + 4CLOCK = 4RESET = 1INIT:OUT PORTBASE, 0SCREEN 12 ‘640 X 480 X 16 COLORSFOR t = 0 TO 15 A& = 65536 * (t * 4) + 256 * (t * 4) + (t * 4) PALETTE t, A&NEXT tDO OUT CONTROL, 32 OR RESET OR CLOCK OUT CONTROL, 32 OR RESET OUT CONTROL, 32 OR RESET OR CLOCK FOR lines = 0 TO VIDLINES - 1 FOR pixel = 0 TO VIDPIX - 1 OUT CONTROL, 32 OR CLOCK OUT CONTROL, 32 data = INP(EPPDATA) PSET (pixel, lines), data / 16 NEXT pixel NEXT lines LOCATE 18, 2 PRINT DATE$ + “ “ + TIME$ IF INKEY$ <> “” THEN SYSTEMLOOPFigure 6 : Le programme de gestion, écrit en QBasic.

Le fonctionnement dans son ensemble

En sachant comment sont faits chacun des deux modules, on peut voir maintenant ce qu’ils font quand ils sont reliés ensemble, en ayant à l’esprit qu’à partir de là, c’est le PC qui prend la main et qui en coordonne l’activité.

Le digitaliseur fonctionne continuellement et de façon autonome.

Il échantillonne le signal vidéo composite et écrit en RAM les données issues de la conversion.

Pour lire les données écrites dans la mémoire, le PC envoie premièrement une impulsion de Reset (par la ligne STROBE).

Puis il envoie des impulsions d’horloge au rythme desquelles il démarre la scrutation séquentielle de chaque octet correspondant aux pixels respectifs de l’image à recomposer.

Chaque octet, élaboré par la routine du soft, est ensuite visualisé, produisant, à un endroit défini de l’écran, un certain niveau de gris. Autrement dit, une certaine brillance de l’écran.

L’ensemble des pixels construit l’image filmée.

La mise à jour des images se fait toutes les deux secondes, ce qui produit un photogramme (frame) toutes les deux secondes. C’est le temps requis pour visualiser chaque vue.

La résolution d’une image noir et blanc est maximale. Celle-ci est de 400 x 300 points, bien que l’écran la restitue au format 640 x 480.

La définition est sur 16 niveaux de gris.

La raison de toutes ces précisions deviendra plus évidente dans un instant, lors de l’examen du contenu du programme écrit pour la gestion du système (voir figure 6).

Figure 7 : Schéma d’implantation des composants de la carte de test.

Figure 7 : Schéma d’implantation des composants de la carte de test. Figure 8 : La carte de test à montage terminée.

Figure 8 : La carte de test à montage terminée.Le connecteur RCA peut recevoir un signal vidéo composite en provenance de n’importe quelle source vidéo.

Figure 9 : Dessin, à l’échelle 1, du circuit imprimé de la carte de test servant d’interface entre le digitaliseur et le PC.

Figure 9 : Dessin, à l’échelle 1, du circuit imprimé de la carte de test servant d’interface entre le digitaliseur et le PC.Liste des composants

R1 = 150 Ω

R2 = 150 Ω

C1 = 220 μF 25 V électrolytique

C2 = 10 μF 16 V électrolytique

C3 = 100 nF multicouche

U1 = Intégré CD40106

U2 = Régulateur 7805

D1 = Diode 1N4007

Divers :

1 Support 2 x 7 broches

1 Prise RCA pour ci

1 Prise alimentation pour ci

1 Connecteur DB25 mâle pour ci

1 Connecteur strip femelle

19 pôles

1 Connecteur strip mâle

2 pôles

1 Cavalier

1 Circuit imprimé réf. S367

Figure 10 : La liaison au PC se fait sur le port parallèle par un connecteur mâle SubD 25 points.

Figure 10 : La liaison au PC se fait sur le port parallèle par un connecteur mâle SubD 25 points.La carte utilise les 8 bits de données de la LPT plus quelques-uns des signaux faisant partie du standard EPP (Enhanced Parallel Port).

Le programme

Les premières instructions concernent la définition des variables utilisées.

Plus précisément, 400 représente le nombre de colonnes constituant une image (VIDPIX), 300 représente le nombre de lignes (VIDLINES), &H378 représente l’adresse de base du port parallèle (PORTBSE = &H378). Puis viennent les trois registres associés à ce port : le Control Register, le Data Register et le Status Register.

Enfin, nous associons le mnémonique RESET à la ligne 1 du port parallèle, et le mnémonique CLOCK à la ligne 4.

L’instruction SCREEN définit le mode de fonctionnement de l’écran. Elle définit la résolution. Ici, elle est de 640 x 480 x 16 couleurs.

Les couleurs sont redéfinies par l’instruction PALETTE du Basic.

Vous remarquerez au passage que de cette façon, le maximum des couleurs possibles est 16, et que 16 est aussi le nombre maximum des niveaux de gris.

Après les indispensables déclarations et les configurations, on passe au programme proprement dit. Celui-ci est en fait constitué d’une boucle entre DO et LOOP.

A l’intérieur de cette boucle, il y a l’instruction INKEY$ qui fait arrêter l’exécution du programme lorsqu’on appuie sur une quelconque touche du clavier.

Le cycle démarre par l’envoi d’un état logique haut sur la ligne de Reset (STROBE) et sur celle de Clock (INIT).

Le pas suivant prévoit le maintient à l’état haut du Reset, et la mise à zéro du Clock.

Puis l’un et l’autre sont mis à zéro.

Ces commandes constituent en fait un cycle qui permet d’effectuer la mise à zéro des lignes d’adresses de la RAM à deux pages, pour que le digitaliseur y accède à partir de l’adresse zéro.

En effet, pour effacer la mémoire, une simple impulsion positive sur la patte Reset ne suffit pas. Il faut y associer une transition 0/1 sur la patte du Clock, alors que Reset est encore à 1.

Après l’initialisation de la mémoire (mise à zéro du compteur d’adresses), commence l’extraction des données : à chaque cycle d’horloge (0/1 logique) obtenu par les instructions OUT CONTROL, 32 OR CLOCK (Clock = 1) et OUT CONTROL, 32 (Clock = 0), on lit l’octet disponible sur le bus des données D0 à D7 du port parallèle.

L’octet lu sur ces lignes est stocké dans la variable “data” par l’instruction data = INP (EPPDATA).

Puis vient l’instruction PSET qui traite le pixel selon l’état de ses 8 bits, en choisissant les couleurs sur la base d’une palette noir et blanc, c’est-à-dire limitée à 16 combinaisons. C’est la raison pour laquelle l’octet est divisé par 16.

En effet (256 : 16) = 16.

Dès lors, l’instruction NEXT pixel lance un nouveau cycle : nouveau coup d’horloge, acquisition d’un nouvel octet, division et affichage d’un autre point.

Le tout pendant le nombre de fois défini par VIDPIX (ici 400) correspondant au nombre de pixels formant une ligne image.

Après l’affichage de la première ligne, on passe à la deuxième, et ainsi de suite. Jusqu’à ce que le programme atteigne VIDLINES : la dernière ligne.

Les instructions LOCATE 18,2 et PRINT DATE$… servent à faire apparaître à l’écran la date et l’heure courante, sur la base de l’horloge interne du PC.

Plus précisément : LOCATE précise à quel endroit la ligne doit s’écrire, alors que PRINT provoque l’affichage de la date et l’heure, en noir et blanc.

Réalisation pratique

Une fois imprégnés de la façon dont vont les choses, tant pour ce qui concerne la partie électronique que pour ce qui concerne le programme, on peut passer à la réalisation pratique.

Le circuit imprimé de cette carte est un simple face à réaliser par photogravure, en partant d’une photocopie sur mylar du tracé donné tel quel en figure 9.

Vous monterez les composants en partant des plus bas pour terminer par les plus hauts, en vous référant au schéma d’implantation des composants de la figure 7 et à la photo du montage terminé de la figure 8.

En réalité, il y a peu de composants à souder.

Aussi vous commencerez par les résistances et la diode D1 dont il faut respecter les polarités.

Continuez avec le support du circuit imprimé U1 (CD40106) dont le détrompeur doit être tourné du côté du petit strap. Puis soudez les condensateurs.

Pliez les pattes du régulateur U2 afin de le monter à plat (attention au trou de fixation).

Fixez à l’aide d’une vis, rondelle et écrou. Soudez.

Puis installez le connecteur mâle SubD 25 points coudé pour circuit imprimé.

Poussez-le à fond avant de commencer à le souder, afin de lui assurer la meilleure tenue mécanique.

Pour ce qui concerne l’alimentation, comme vous utiliserez vraisemblablement un bloc secteur, vous installerez une embase à souder de type adapté.

L’entrée vidéo se fait sur une embase RCA pour circuit imprimé.

N’oubliez pas les deux straps. Ni le cavalier J1, placé derrière l’embase RCA. Vous veillerez à le laisser normalement fermé.

Les figures 9, 10 et 11 montrent le résultat auquel vous devriez arriver.

Reliez ensuite cette carte à celle du module digitaliseur, avec laquelle elle forme une sorte de sandwich. Puis effectuez tous les branchements.

La liaison au PC se fait au moyen d’un câble imprimante à 25 conducteurs.

Pour ce qui concerne le programme, avant d’en essayer un de votre cru, recopiez le nôtre en utilisant l’éditeur du DOS, dans un fichier auquel vous donnerez un nom (celui que vous voulez), terminé impérativement par l’extension .BAS.

Puis, toujours sous DOS, appelez QBasic suivi du nom du fichier que vous avez donné au programme.

Une fois le fichier ouvert avec QBasic, lancez-le par la commande RUN.

Dès lors vous verrez les images venir à l’écran, en haut à gauche, avec, dans le bas, la date et l’heure. Les images sont mises à jour toutes les deux secondes.

Pour arrêter la visualisation des images, il suffit d’appuyer sur une quelconque touche du clavier, ce qui provoque la sortie du programme, et le retour à QBasic et à l’environnement DOS.

Figure 11 : La carte de test et le module digitaliseur se placent l’un sur l’autre et s’interconnectent au moyen de broches mâles et de contacts femelles.

Figure 11 : La carte de test et le module digitaliseur se placent l’un sur l’autre et s’interconnectent au moyen de broches mâles et de contacts femelles.

Aucun commentaire:

Enregistrer un commentaire